手邊有一台早期獲得的 Altera DE2-115 開發平台 ,一直放著積灰塵也不是辦法,再加上最近想多玩玩 FGPA,所以就來重新玩一次吧 :)

和 Xilinx Zybo Board 不同,Altera DE2-115 開發平台 是只有 FPGA 的開發板,並未包含 ARM Cortex-A9 來作為輔助用的 CPU,對於只想學 FPGA 的人而言,這算是不錯的平台,想要 CPU 的話,就自己寫個 CPU 上去或是用 NIOS-II 軟核 CPU 就好了。

總之,就讓我們來玩玩這一片早期的 FPGA 開發板吧 (想當年這一片可是要台幣 3W 的呢!)

不過在我們開始這一切之前,我們需要稍微了解一下這片開發板以及他的週邊等資訊。

要了解 Altera DE2-115 開發平台 的相關資訊,我們首先先到他的開發商 友晶科技 網站去下載 DE2-115 User Manual ,這本手冊會帶領我們了解這平台相關的週邊。

注意到這邊會刻意忽略掉 High Speed Mezzanine Card (HSMC) 接口,因為這個接口除非去買擴展板,不然對一般人而言不會有用到的機會。

基本硬體認識

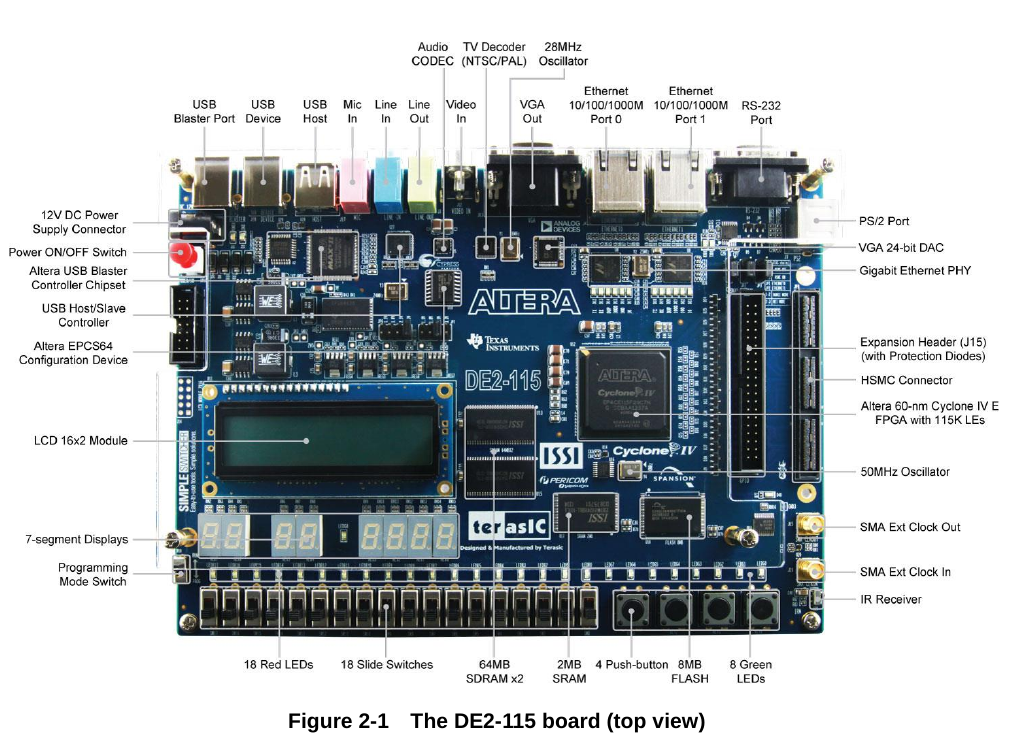

拿到手的 DE2-115 就像這個樣子,從正面來看:

哇,這片板子週邊有夠多的,難怪不便宜,不過細節我們待會在說吧,先來看看背面還有什麼?

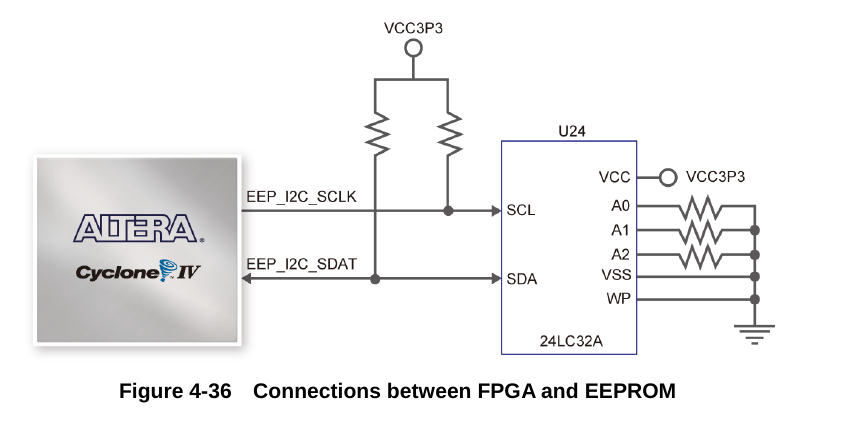

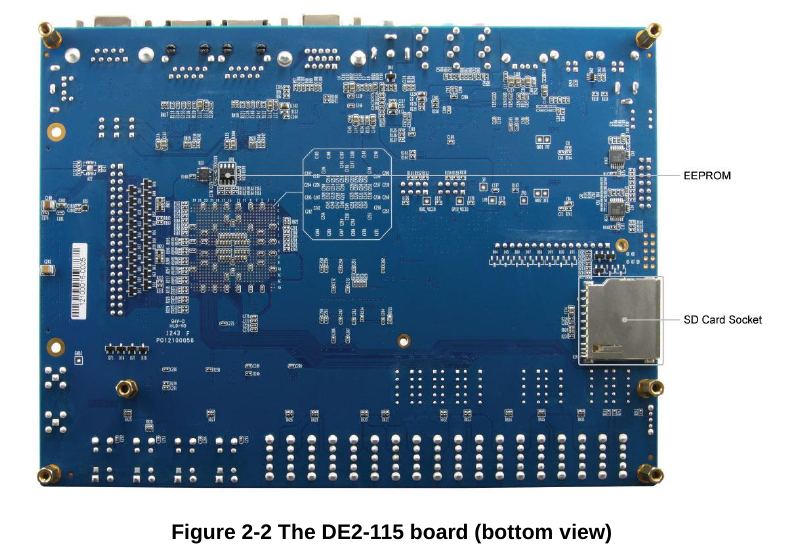

背後偷偷藏了一顆 EEPROM,未來我們有資料要存放的時候就需要他了!

了解了基本板子週邊後,接下來要來一個一個的研究吧~

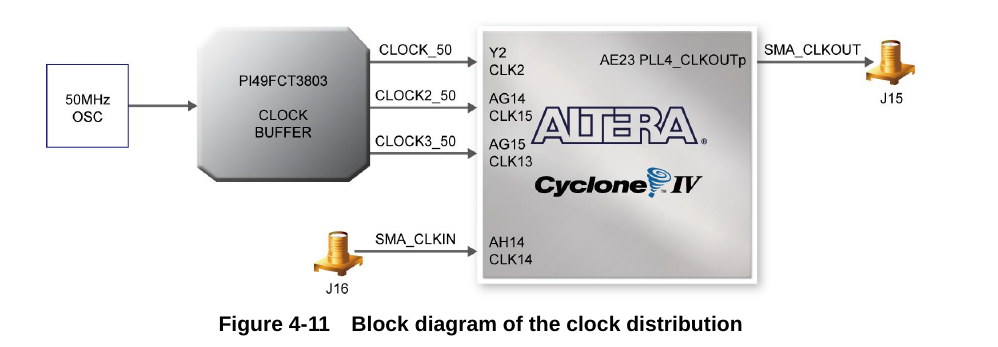

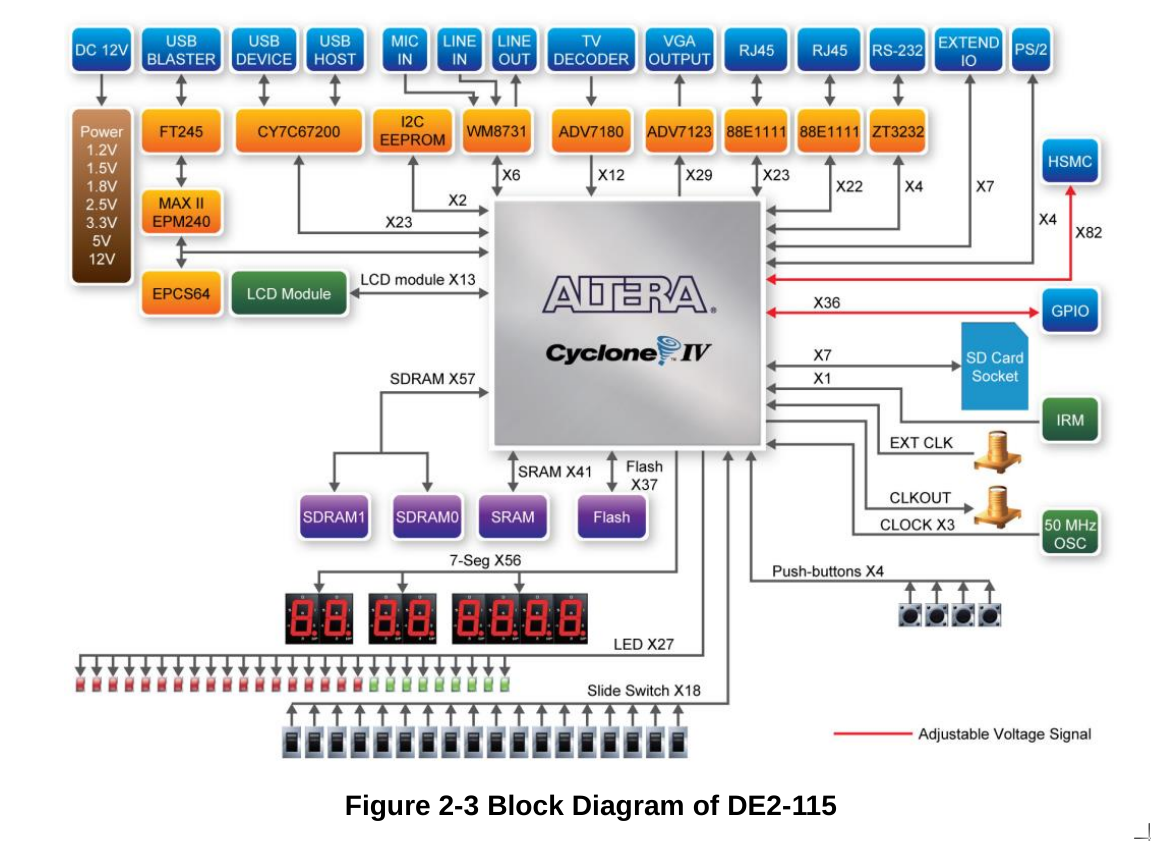

方塊圖

上面的週邊資訊太複雜了,好在 DE2-115 User Manual 有提供方塊圖 (Block Diagram) 可以讓我們對這平台用的 IC 以及有的功能再進一步的了解

FGPA 核心

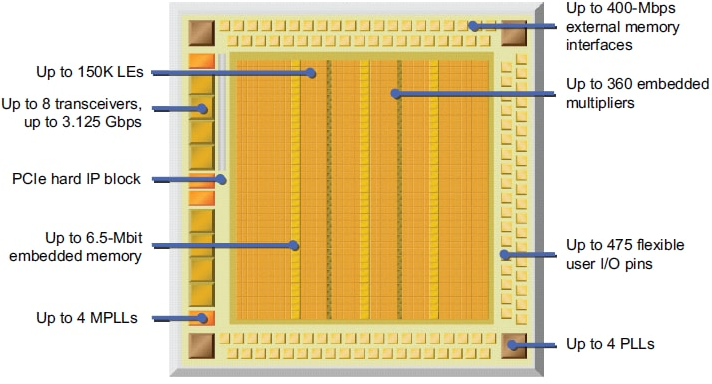

DE2-115 使用的 FPGA 核心是 Cyclone IV EP4CE115F29 ,是屬於 Cyclone IV 系列的,當然在一開始玩的時候只需要知道這個是哪個系列,可以裝下多少邏輯閘就夠了。

因此,就讓我們列一下這顆 FPGA 到底有多少能耐:

- 114,480 LEs (邏輯單元)

- 432 M9K 記憶體模塊

- 3,888 K bits 嵌入式存儲器

- 4 PLLs (鎖相迴路)

嗯… 看不懂,就只好引用一下 Mouser 上的圖啦 ~

這邊跳過部份資訊,如果想搞懂關於這顆 FPGA 的描述,包含 LE 是啥啦之類的,推薦看一下 FPGA 芯片内部硬件介绍 的說明。

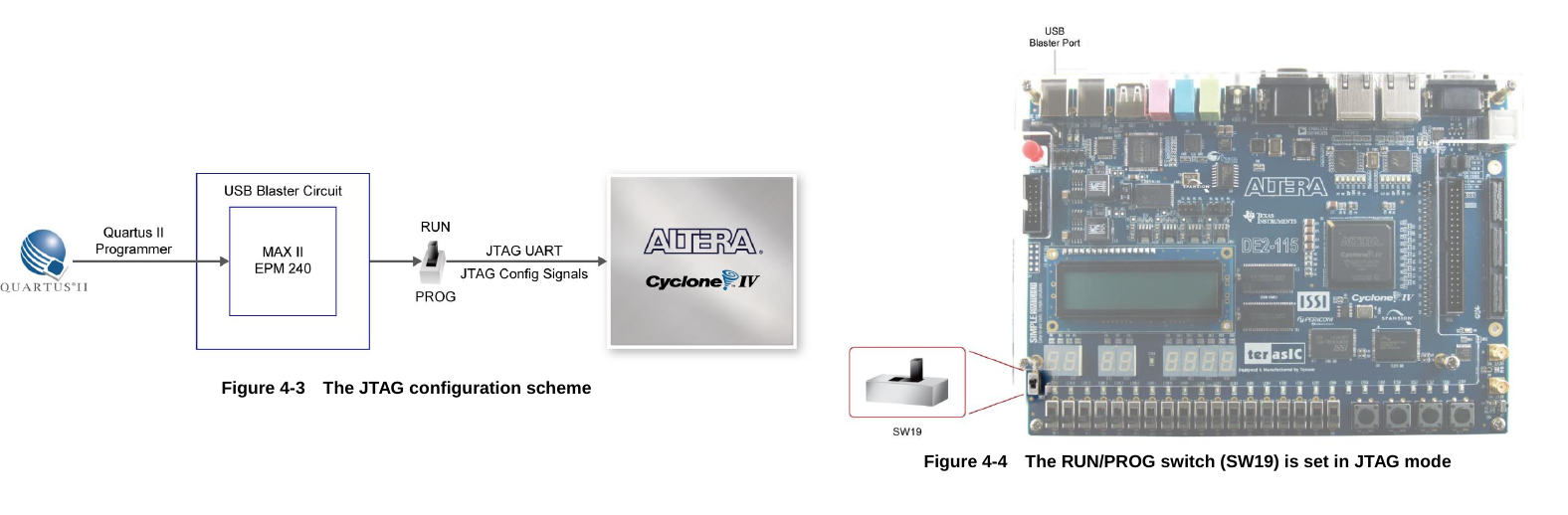

JTAG

JTAG 是 DE2-115 上用來下載程式到 FPGA 用的界面,根據設定的不同,我們可以將其分成 JTAG Mode 和 AS-mode,下面就來講解這兩種模式的不同。

簡單的說:

- JTAG mode: 一般下載用,斷電後資料消失。

- AS mode: 下載後,即使斷電資料也會保存。

JTAG mode

JTAG mode 是一般下載用的方式,缺點是斷電後資料不會保存在板子上。如果你想要下載後重新上電可以執行上一次下載的程式的話,請使用 AS mode。

使用 JTAG Mode 的時候,請注意以下步驟:

- 接上電源

- 設定 SW19 在

RUN的位置 - 接上 USB type B 線到 USB Blaster 的位置

- 透過 QUartus II 選擇適合的位元流 (.sof) 檔案進行下載

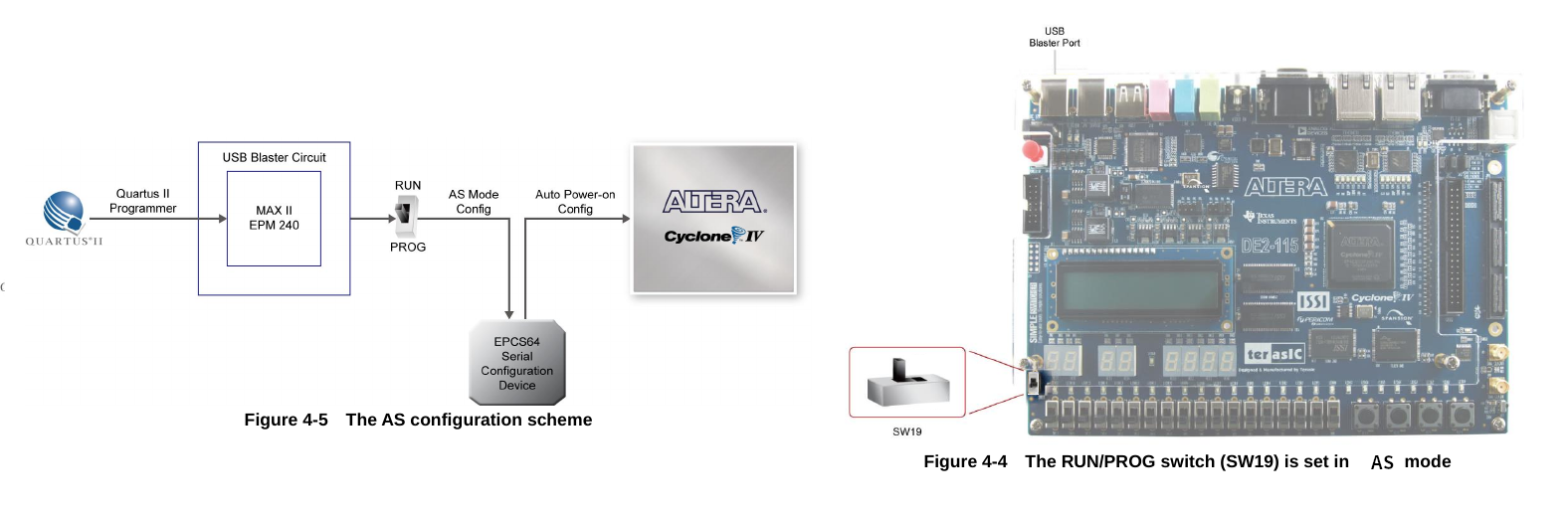

JTAG AS mode

當我們想要斷電再上電後,還可以執行上一次下載的程式的話,這時候就需要透過 AS Mode 來進行。

AS Mode (Active Serial Programming) 會將位元流下載到 EPCS64 這顆串口 IC,該晶片除了可以透過串口 (Serial) 下載外,同時也是一個儲存裝置,可以存放共 64MB 大小的資料。當電源啟動的時候,DE2-115 會從 EPCS64 拉取資料,完成 FPGA 的設定,這也是為何 AS Mode 可以在斷電的情況下保持資料的原因。

使用 AS Mode 的時候,請注意以下步驟:

- 接上電源

- 接上 USB type B 線到 USB Blaster 的位置

- 設定 SW19 在

PROG的位置 - 透過 QUartus II 選擇適合的位元流 (.pof) 檔案下載到 EPCS64

- 下載完成後,將 SW19 切換回

RUN的位置,這樣會讓 DE2-115 在開機的時候抓取 EPCS64 上的資訊。

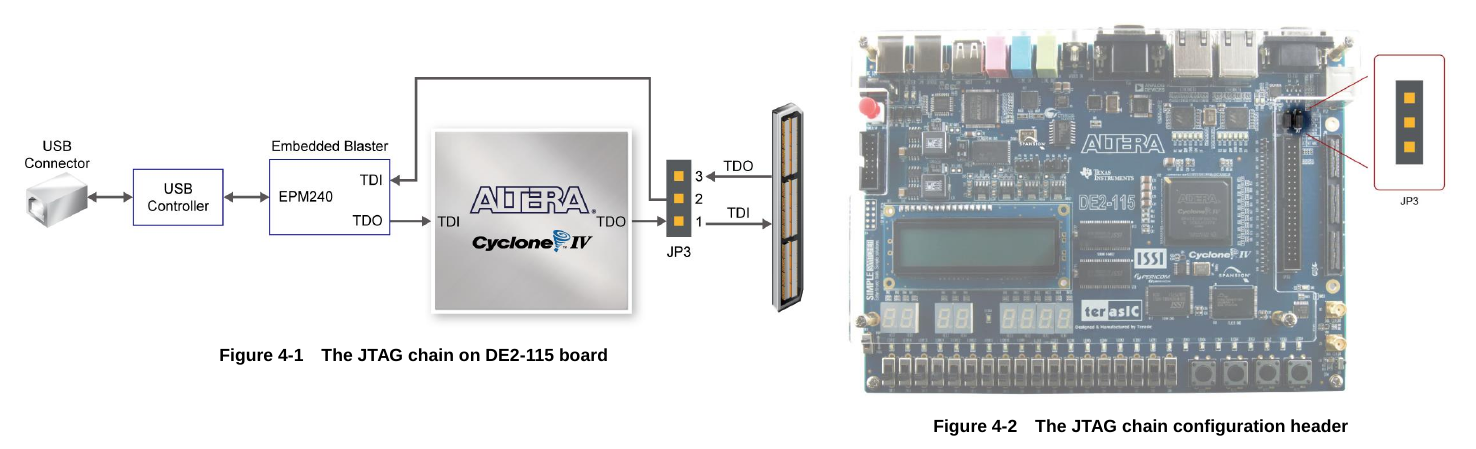

JTAG Chain

除了 JTAG mode 和 AS mode 外,如果我們想要透過 DE2-115 將資訊下載到別的 Altera FPGA 開發板的話,這時候就是使用 JTAG Chain 的時機。

參照上圖,當我們要使用 JTAG Chain 的時候,需要將 JP3 的 pin2 和 pin3 短路,讓 JTAG 訊號可以透過 HSMC 接口出去。

如果 JP3 的 pin1 和 pin2 短路 (預設) ,此時形成一個封閉的迴路,這時候 JTAG 在下載的時候只會偵測到 DE2-115 上的 FPGA 晶片。

按鈕

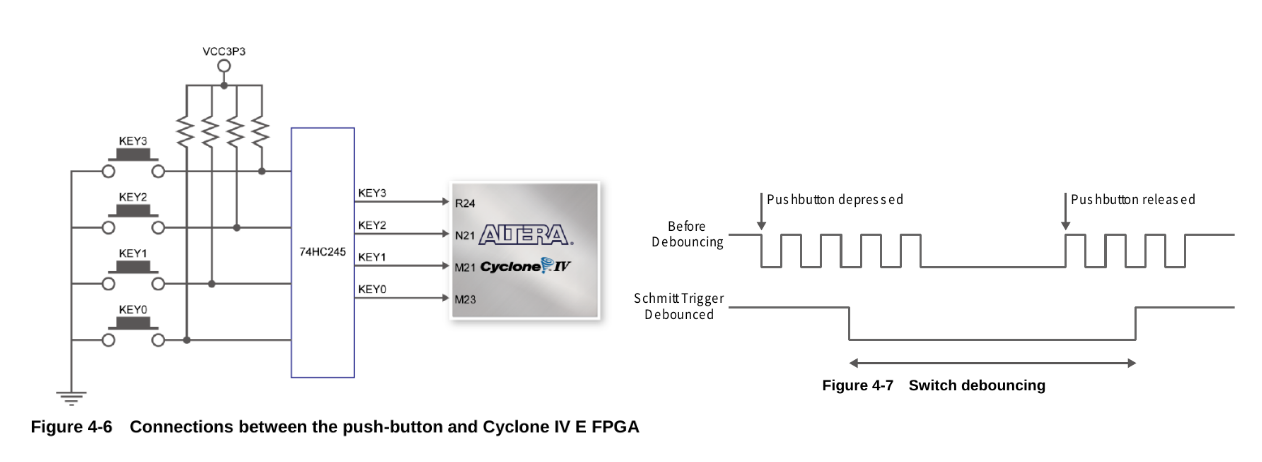

DE2-115 共有四個按鈕 (Push Button),這些按鈕都接上了施密特觸發器(Schmitt trigger)來對按鈕去除彈跳 (debounce)

也因為已經在電路上做了防彈跳功能 (debounce),因此在使用這些按鈕的時候我們就不需要透過軟體去濾掉按下按鈕後產生的那些雜訊。

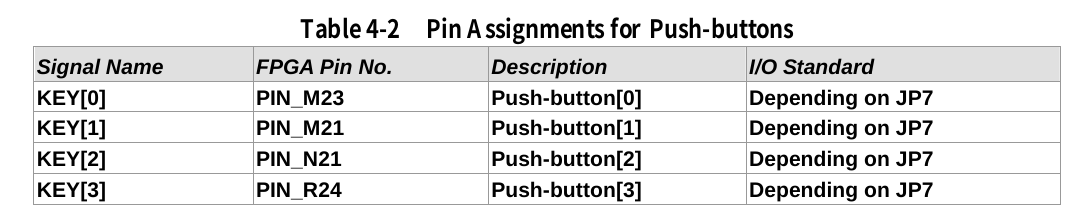

我們可以透過以下的表格,找出 FPGA 對應按鈕的腳位: