在 Ultra96 開發紀錄: 硬體認識 一文中我們了解了 Ultra96v1 這塊開發板的一些資訊後,就讓我們來開始第一個專案吧。

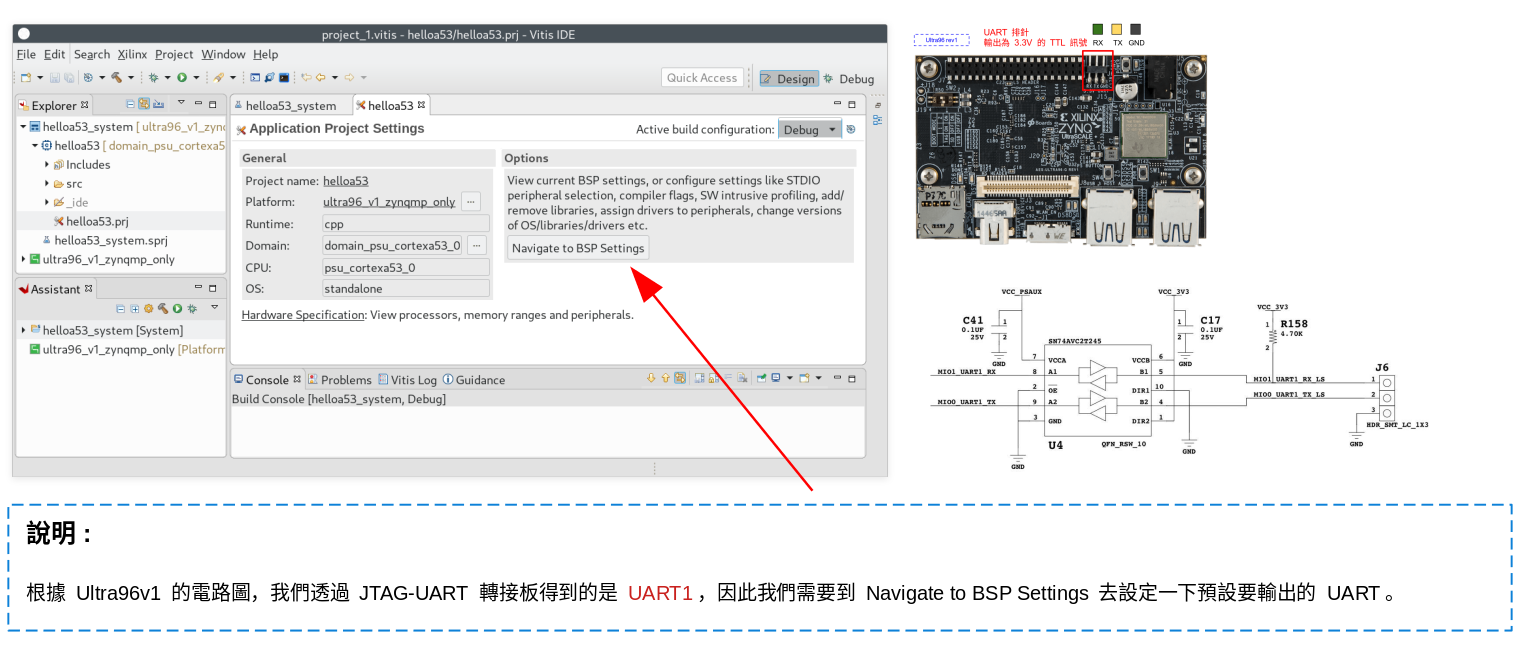

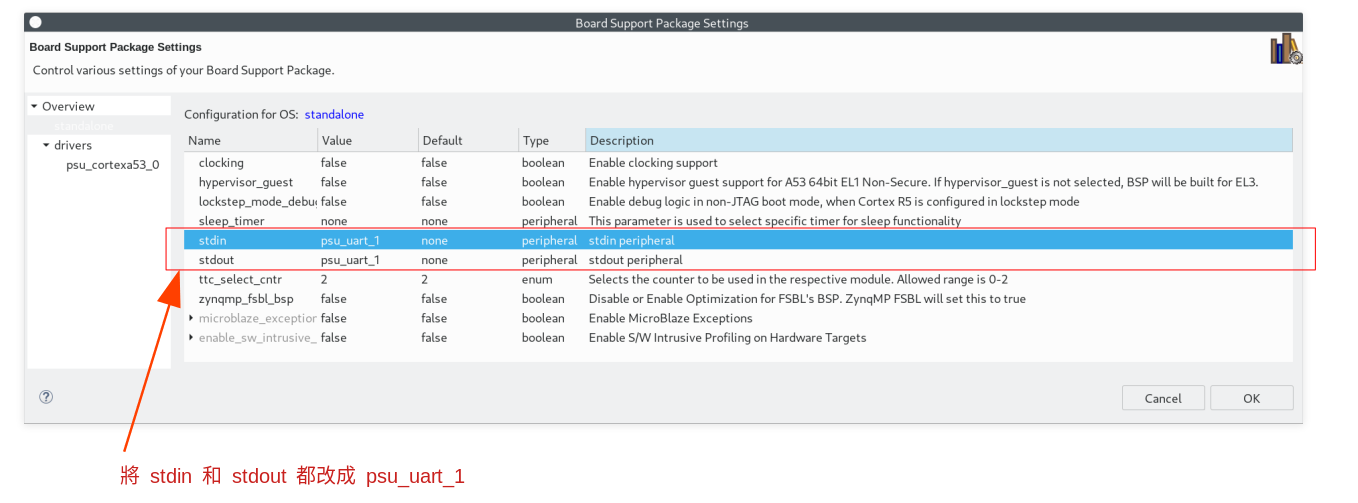

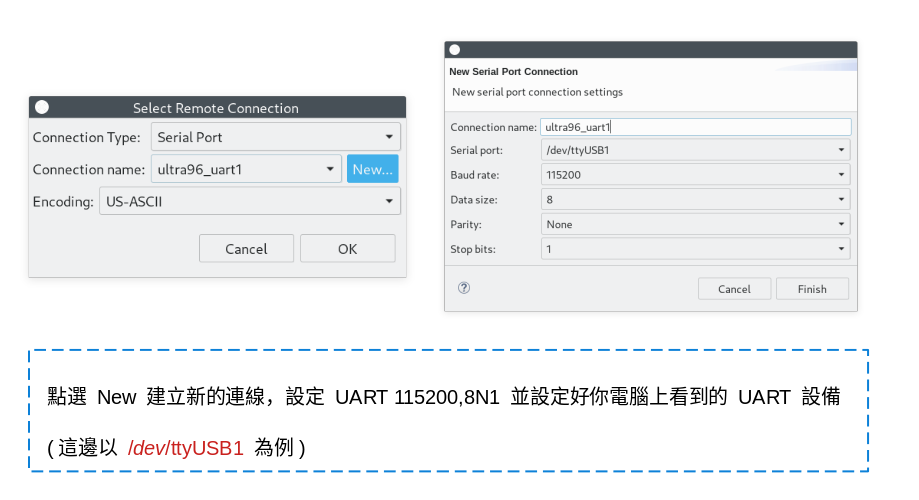

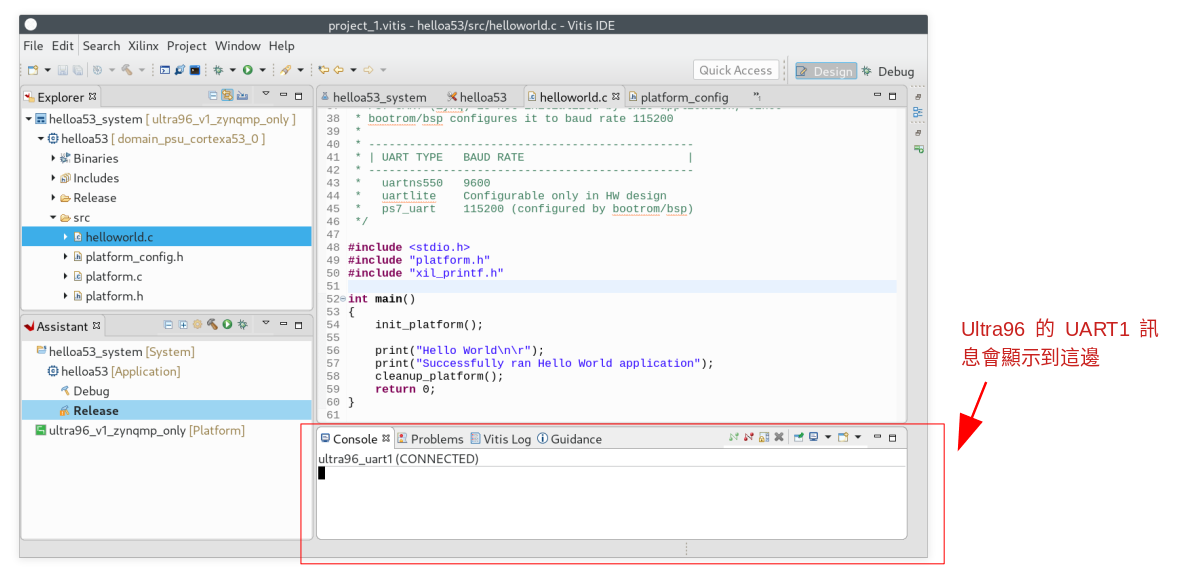

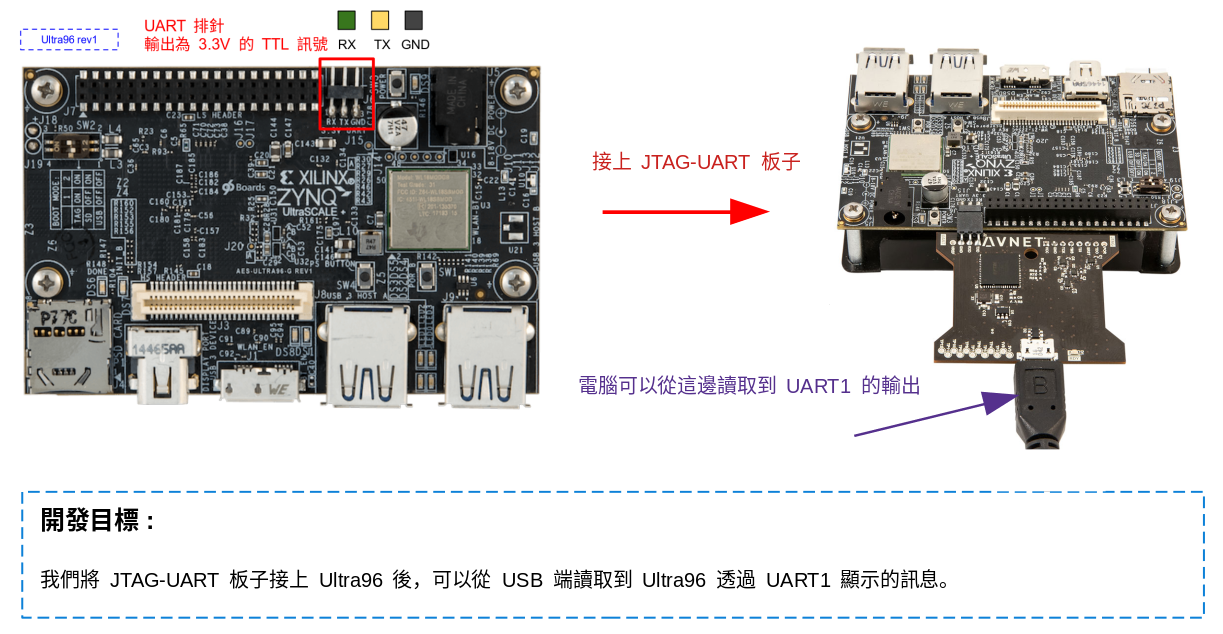

由於 Ultra96 拉出來的低速擴充腳位(Low Speed Expansion Connector)基本上是以 2.0mm 的寬度為主,並且電壓為 1.8V ,不透過擴充板之類的會讓我們不好使用,因此這邊文章將採用傳統的方式,透過 Uart1 來將我們的測試訊息輸出。

(本文以 Vivado 2020.1 進行開發,請注意文中開發板以 Ultra96v1 為主,但可套用到 Ultra96v2 上。)

使用設備

要完成本篇文章所描述的部份,你需要以下幾種器材:

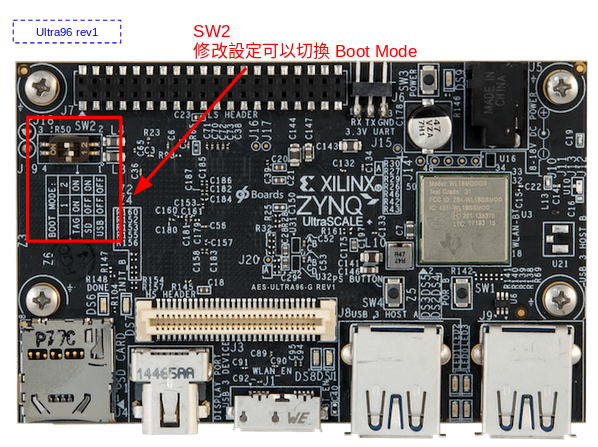

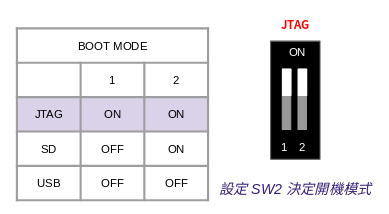

- Ultra96 (rev1 或是 rev2 皆可)

- Ultra96 USB-to-JTAG/UART Pod

開發目標

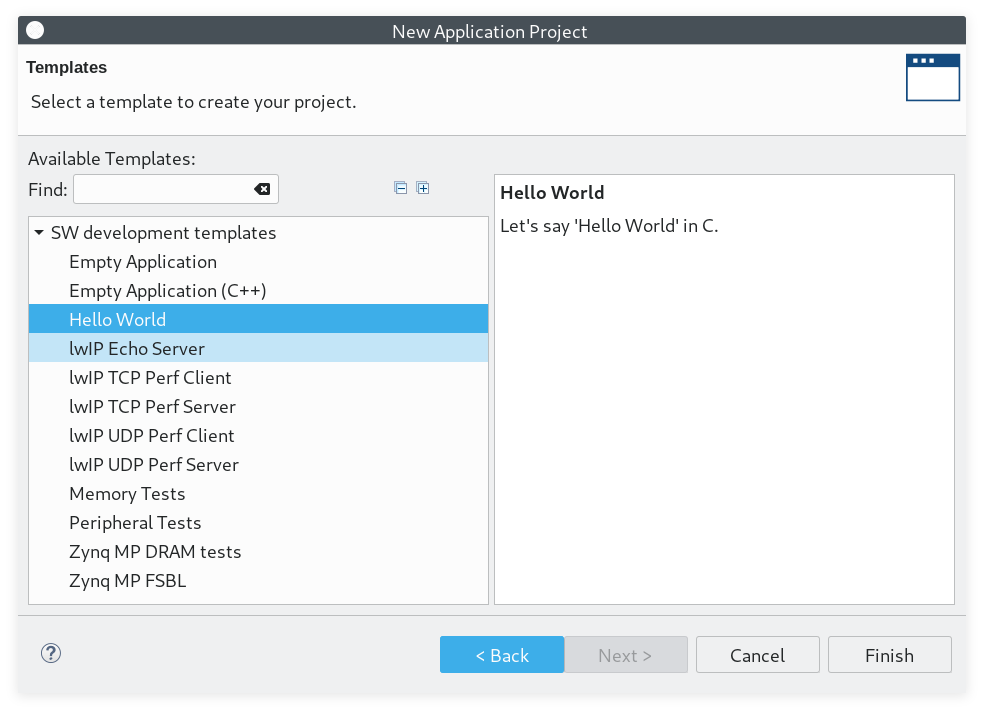

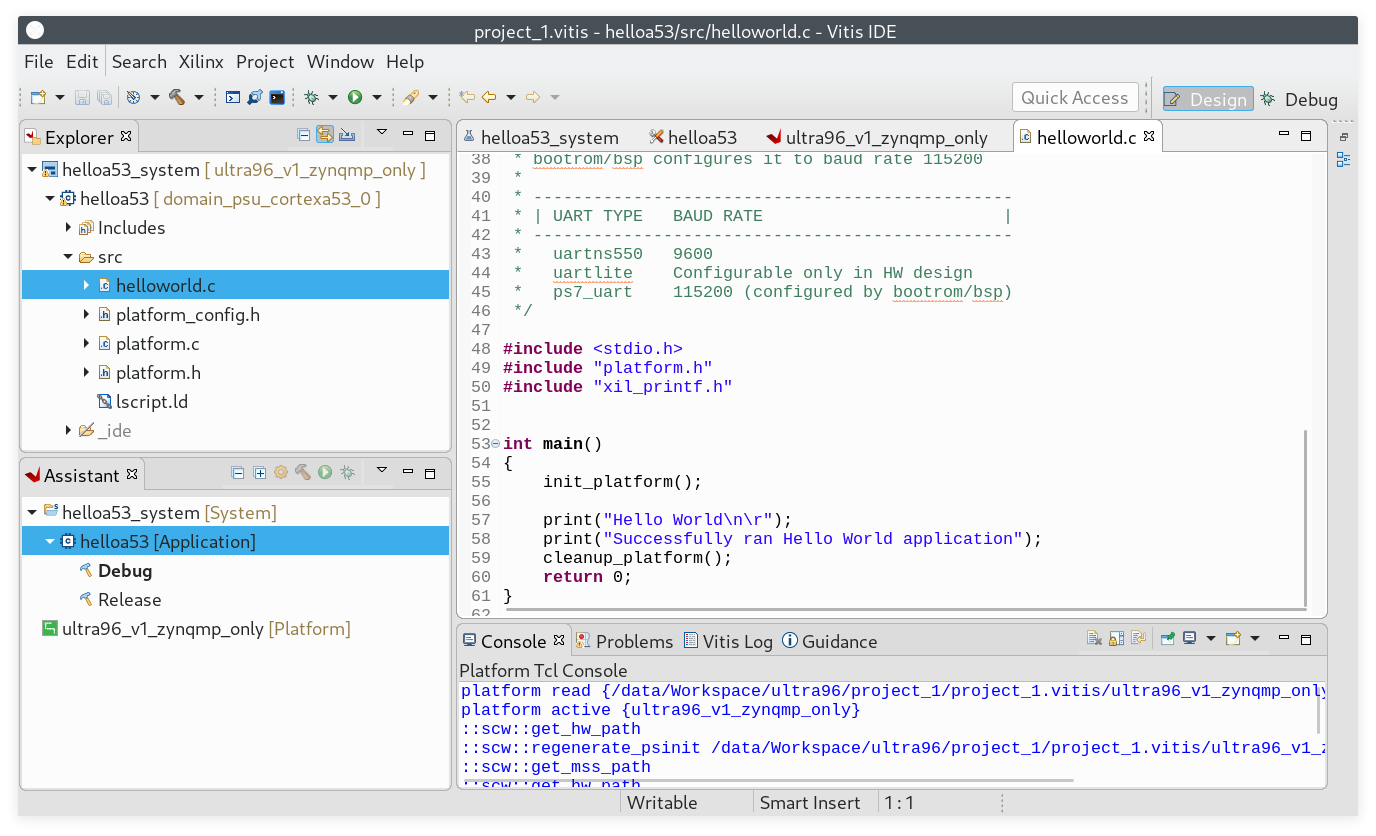

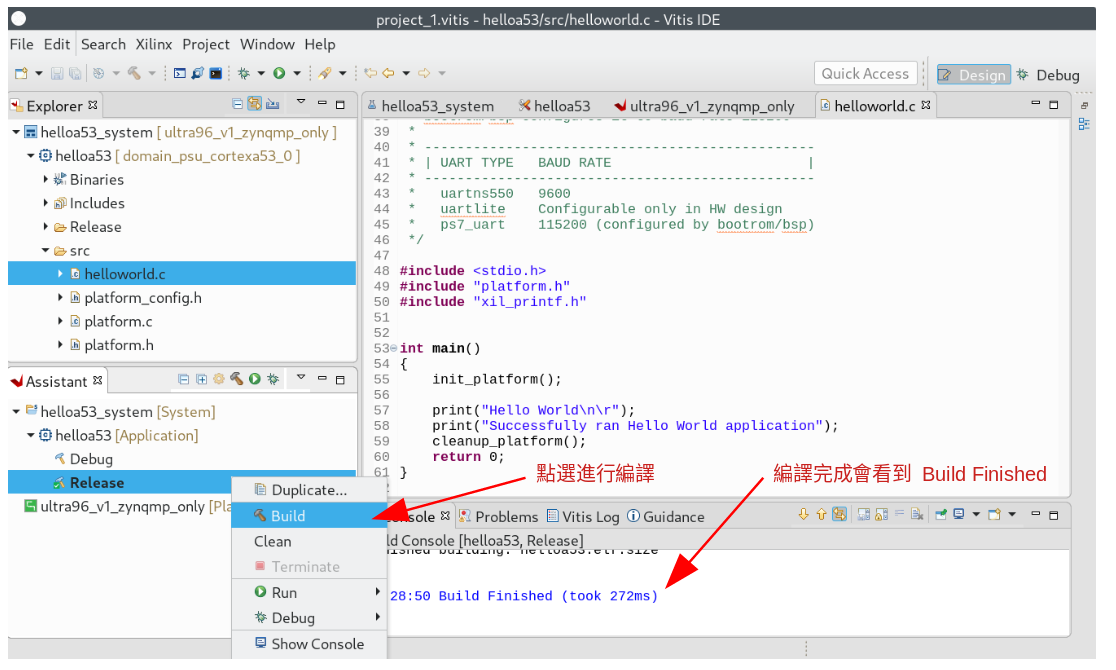

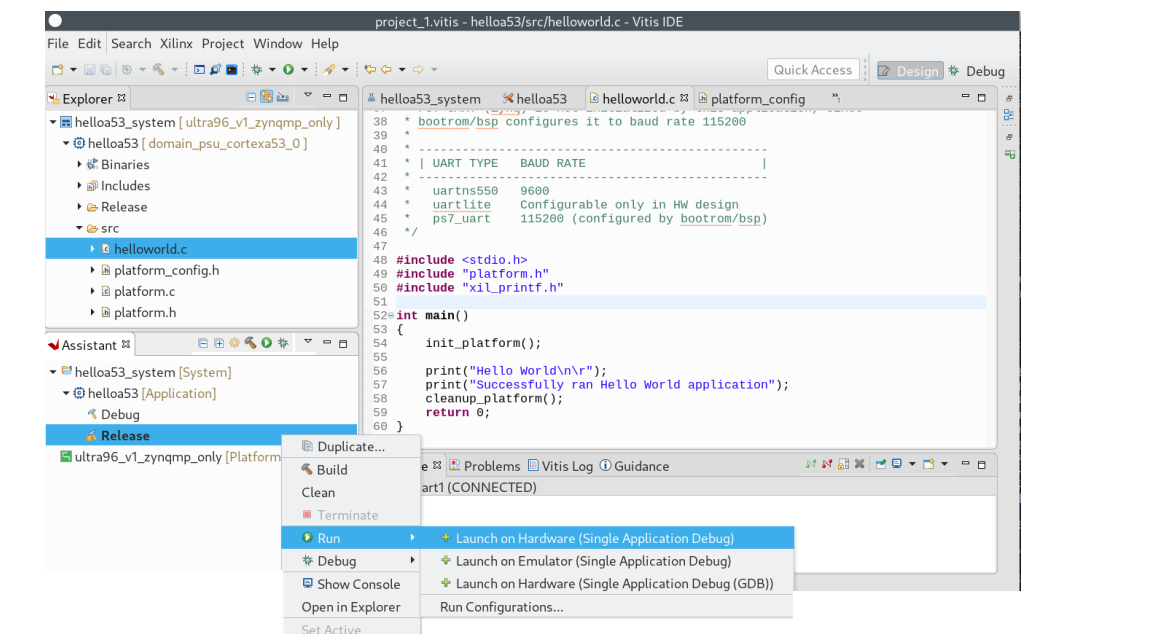

由於這是第一個 Ultra96 的專案,當然是從 Hello World 來開始啦~ 我們將透過 Vivado 建立基本的 Ultra96 的系統,並透過 Vitis 來建立一個會透過 UART1 顯示 Hello World 的簡單程式,你將可以透過 Ultra96 USB-to-JTAG/UART Pod 這邊讀取到顯示的訊息。

建立專案

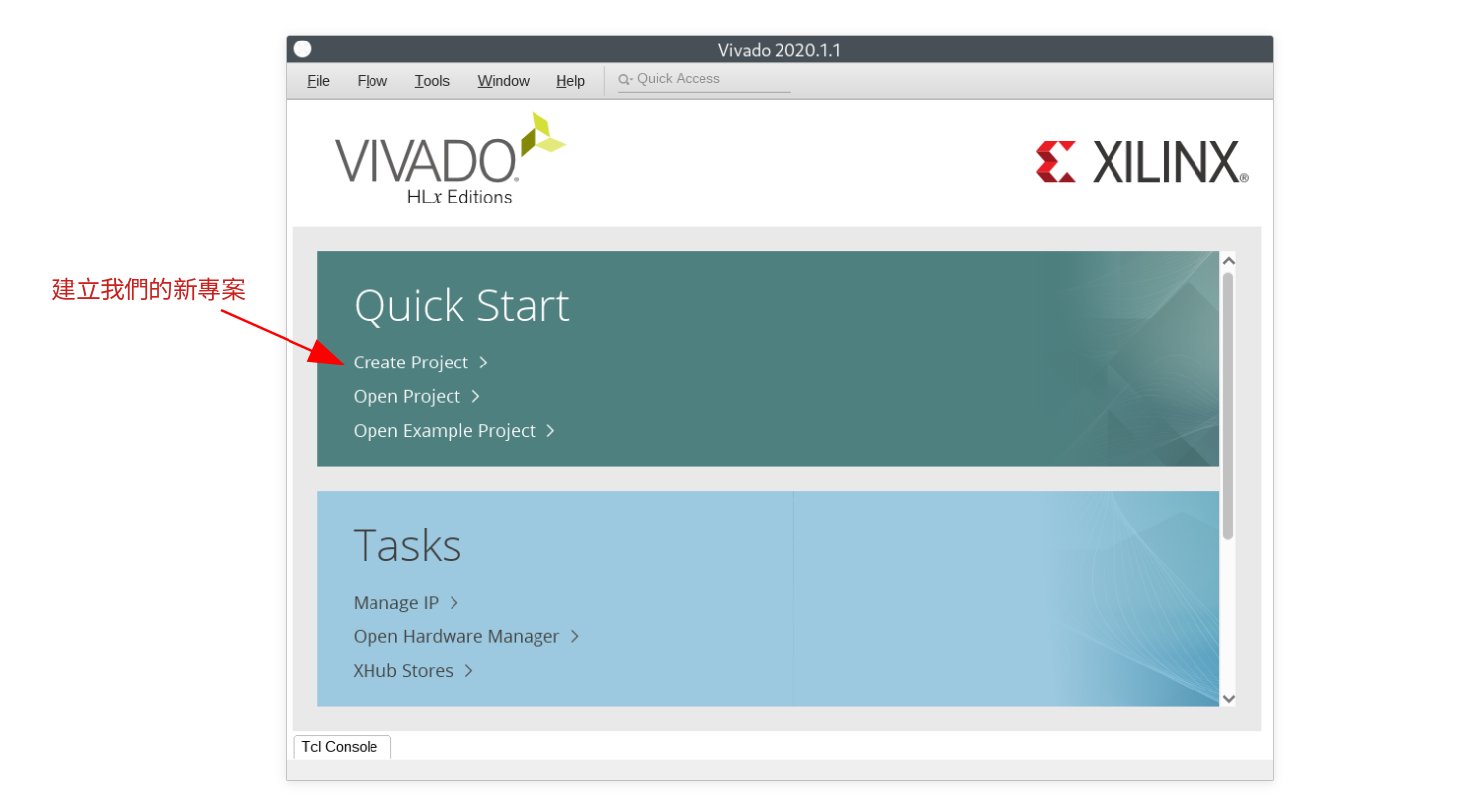

首先讓我們打開 Vivado 吧,請確定在進行這一步之前,有先參照 Ultra96 開發紀錄: 讓 Vivado 有 Ultra96 的設定檔 一文的說明,讓我們在建立專案的時候可以找到 ultra96 這塊開發板。

啟動了 Vivado 後,點選 Create New Project 來建立我們的新專案

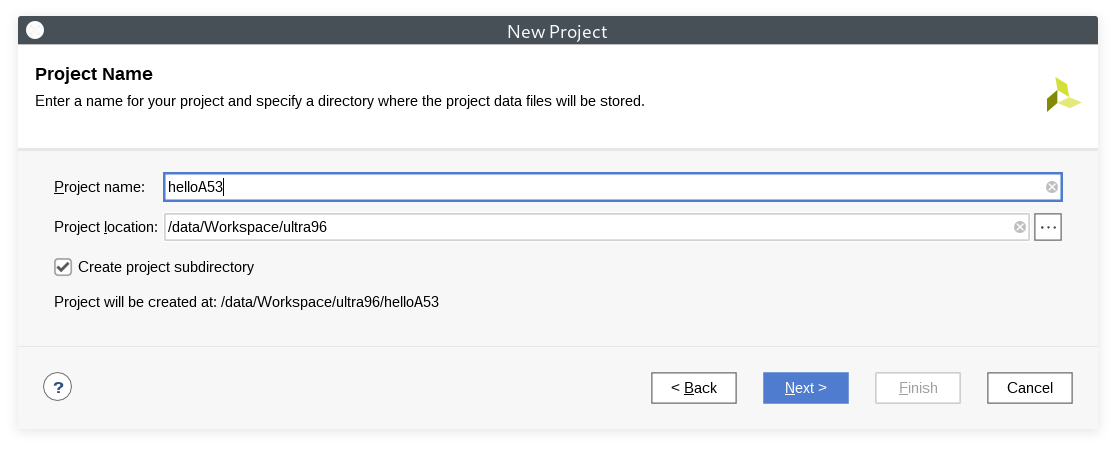

接下來指定好專案路徑和名稱

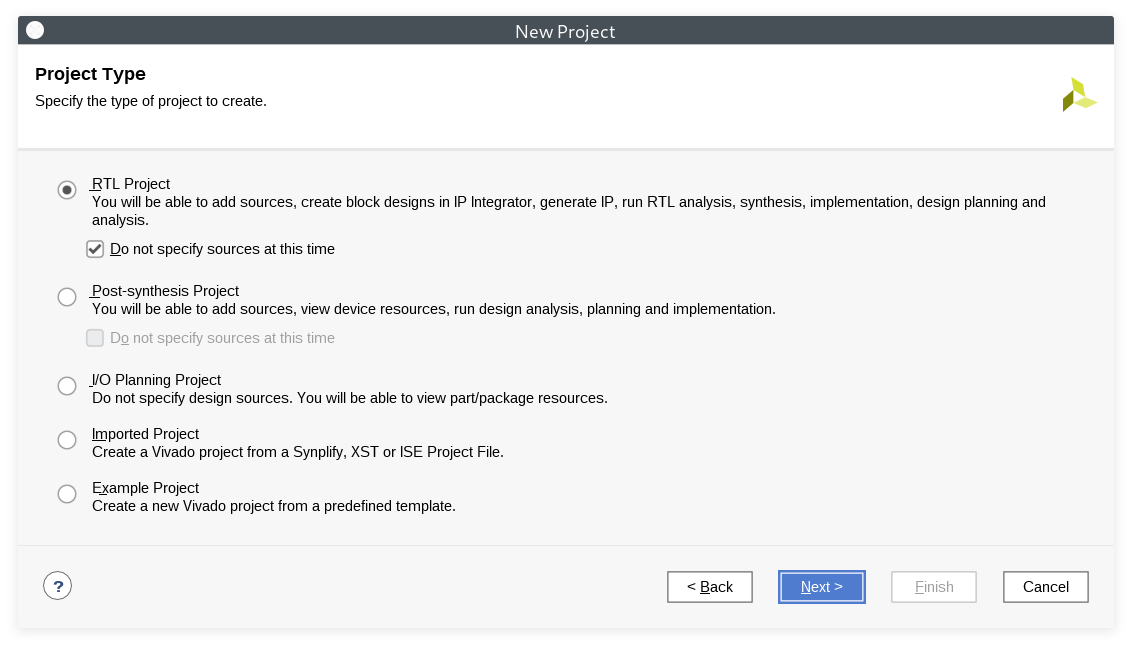

選擇 RTL Project ,由於我們這次不會撰寫硬體描述語言,因此也請勾選 Do not specify sources at this time

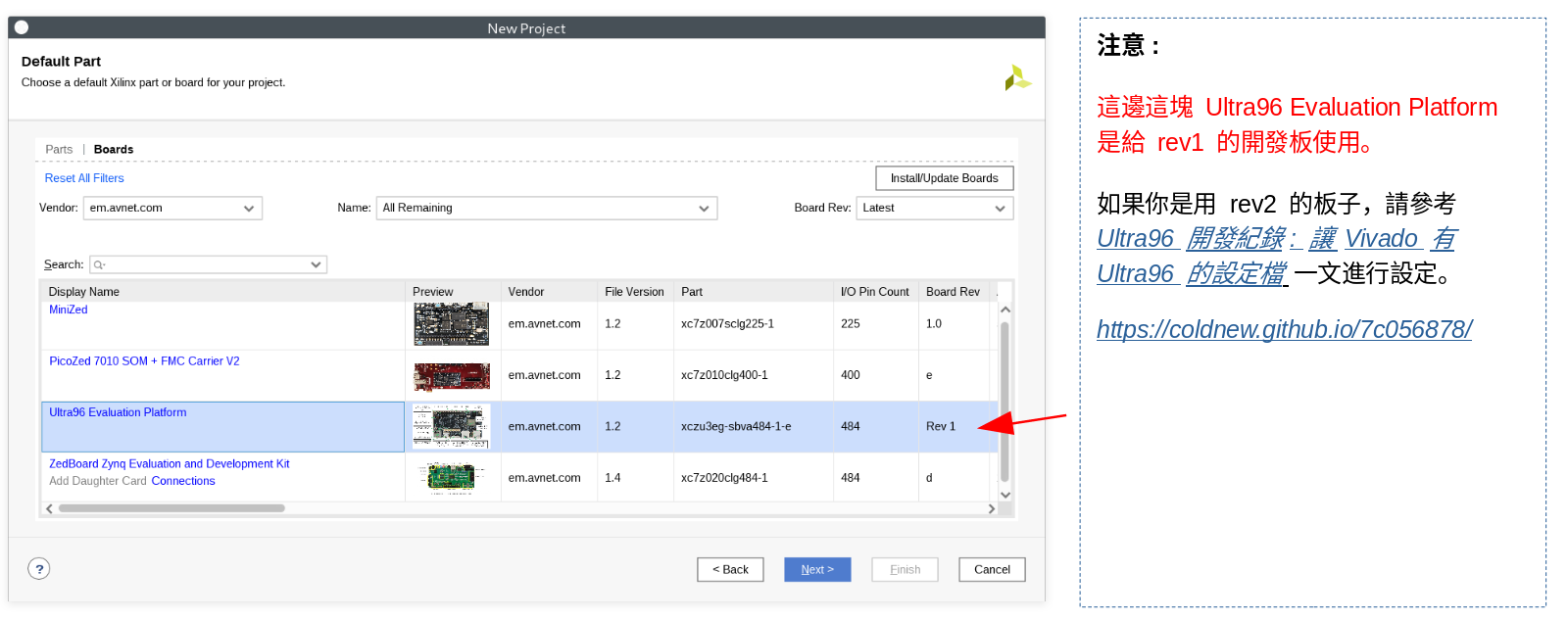

根據你是用 Ultra96v1 或是 Ultra96v2 來選擇你的板子,如果這邊看不到你要找的開發板的話,請再去看一下 Ultra96 開發紀錄: 讓 Vivado 有 Ultra96 的設定檔 一文的說明。

請注意到,截至本文撰寫時間 (2020/09/05),這邊透過 Install/Update Board 仍舊不會看到 Ultra96v2 的身影,因此如果你是 rev2 的開發板的話,請記得安裝對應的 bd 檔 (Board definition)。

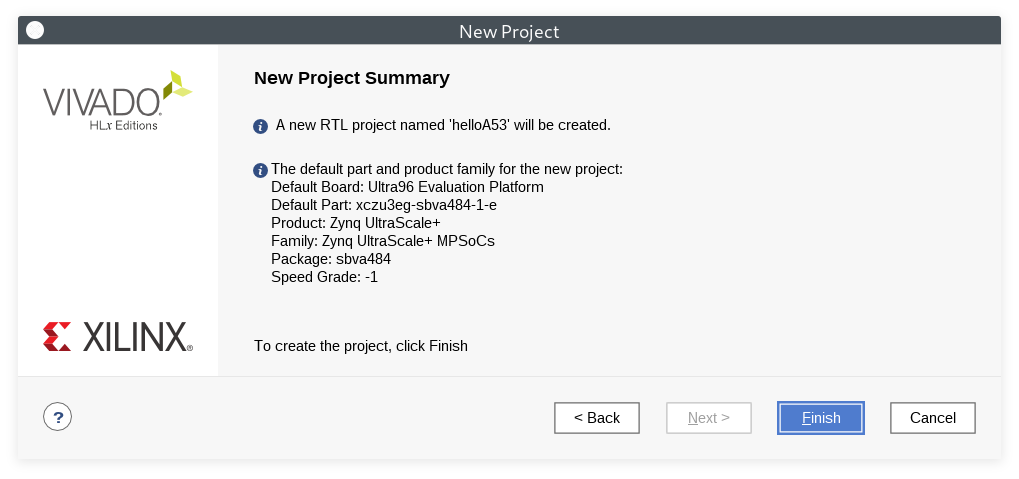

都確定沒問題後,我們就可以來開始我們的專案啦~

建立 Block Design

由於我們的設計需要用到 Xilinx 一些現成的 IP 的時候,就會需要透過 Block Design 來建立我們的電路設計。

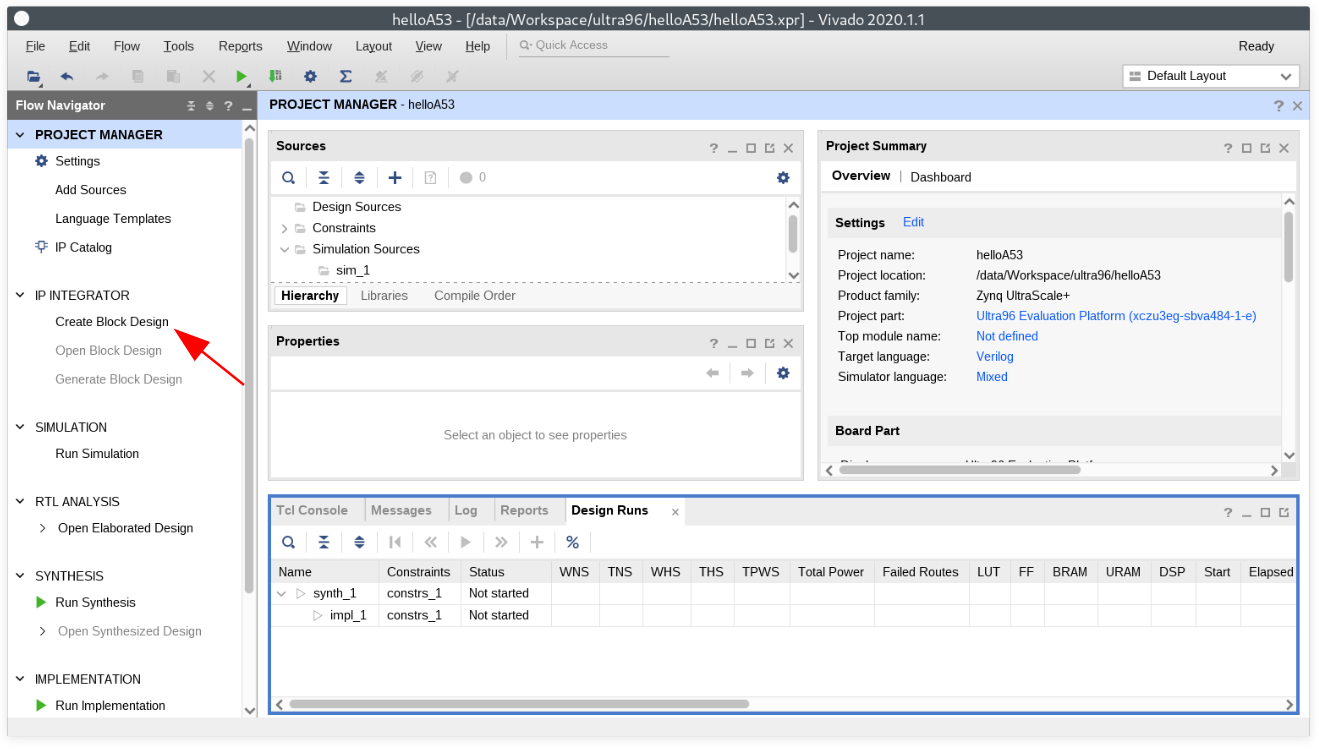

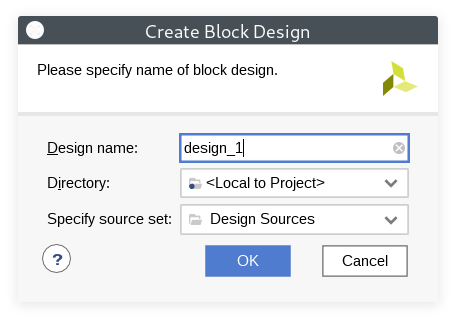

首先點選 IP Integrator -> Create Block Design

接著點選 OK 建立我們的 Block Design

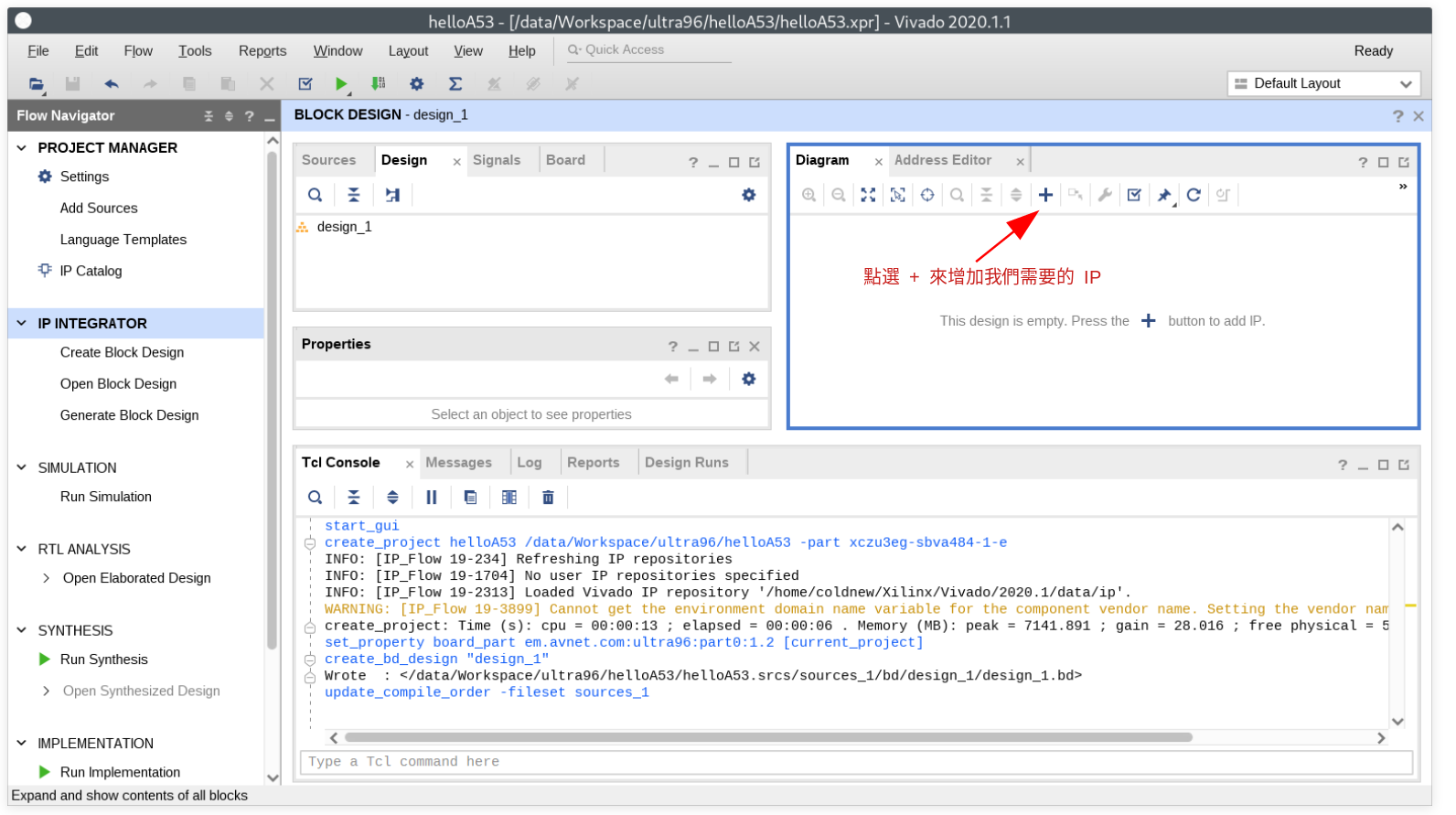

點選 Add IP 按鈕去增加我們需要的 IP

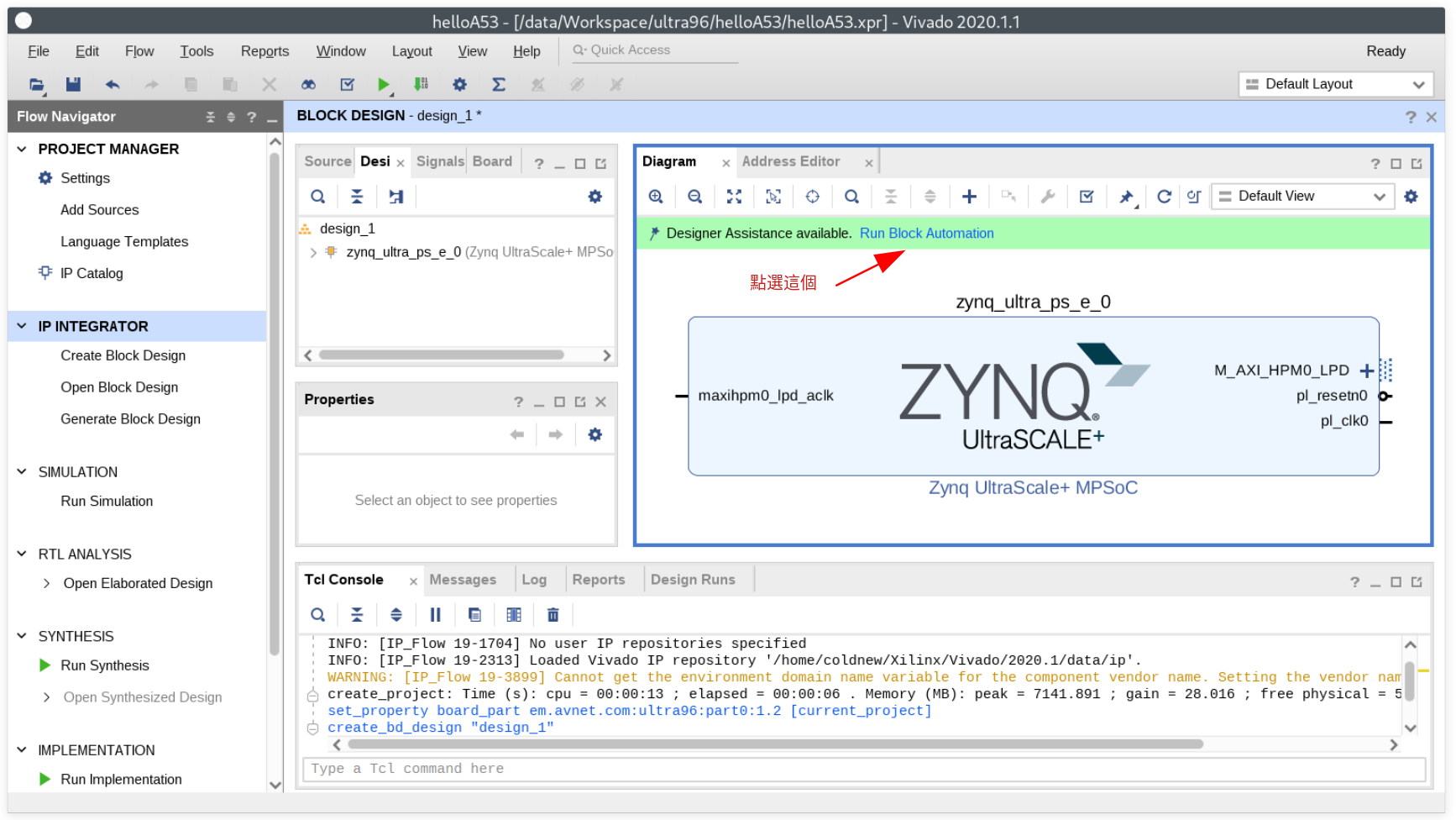

我們首先尋找 Zynq UltraScale+ MPSoC 並將它加入到我們的 Block Design ,並點選 Run BLock Automation 來對該 IP 做一些設定

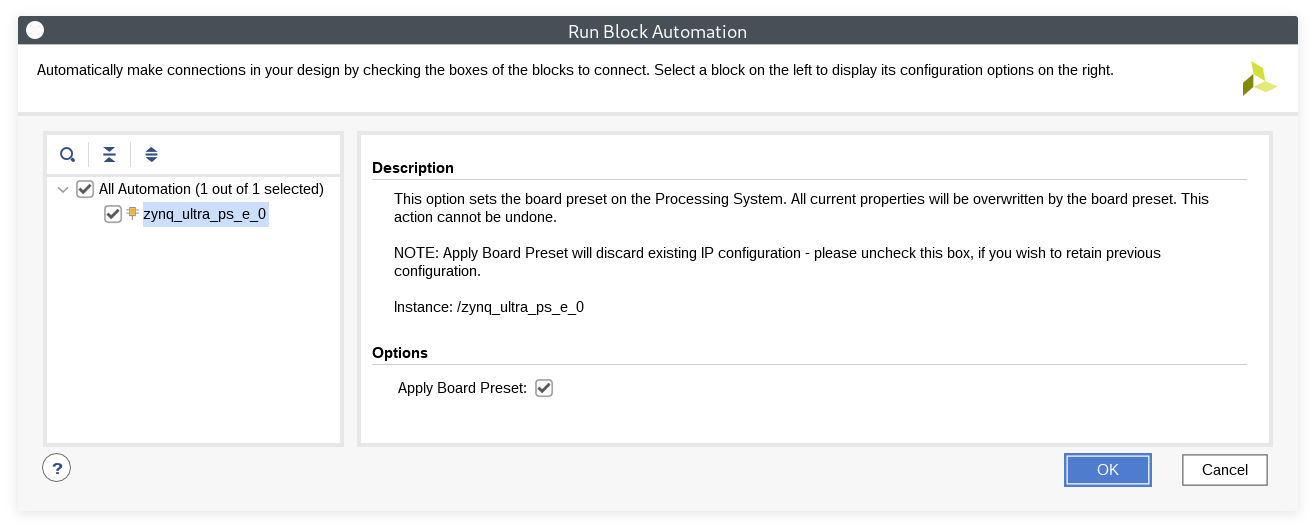

進入到 Run BLock Automation 的設定頁面後,確認 zynq_ultra_ps_e_0 有被勾選到,並且 Apply Board Preset 有被設定起來。

點選 OK 完成設定。

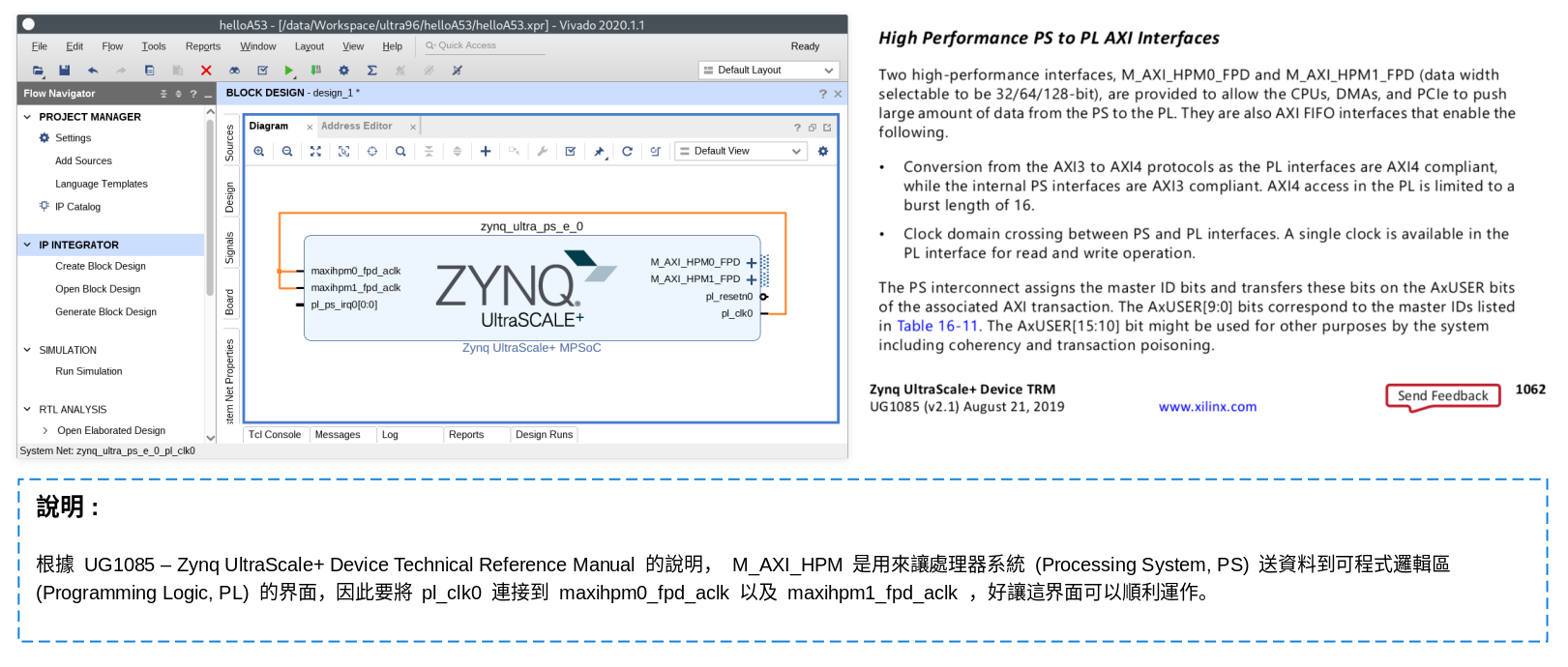

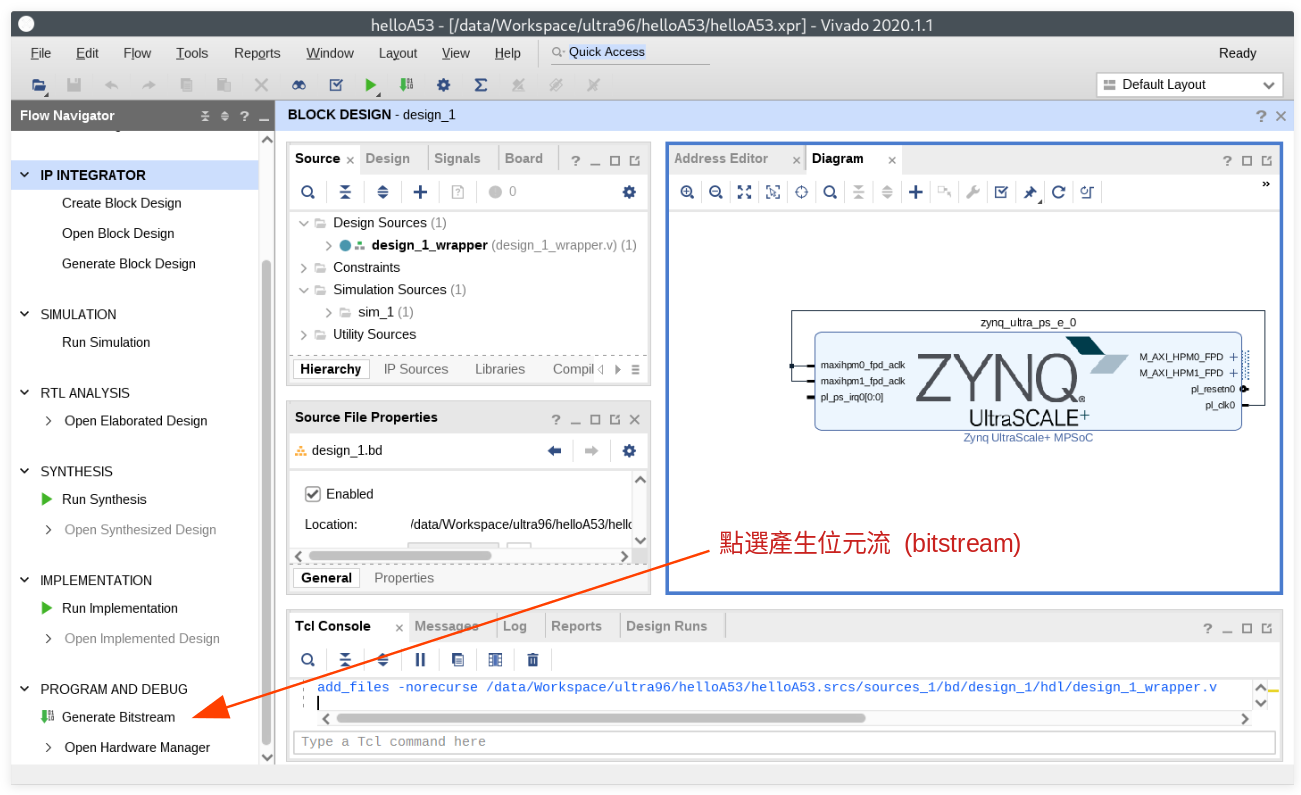

接下來,將 pl_clk0 連接到 maxihpm0_fpd_aclk 以及 maxihpm1_fpd_aclk , 這是為了讓處理器系統 (Processing System, PS) 到可程式邏輯區 (Programming Logic, PL) 之間資料傳送的界面可以順利運作。

(如果你堅持不想將他們接在一起的話,就要知道怎樣關閉 PS to PL AXI Interface, 不然這邊會編譯失敗呦~)

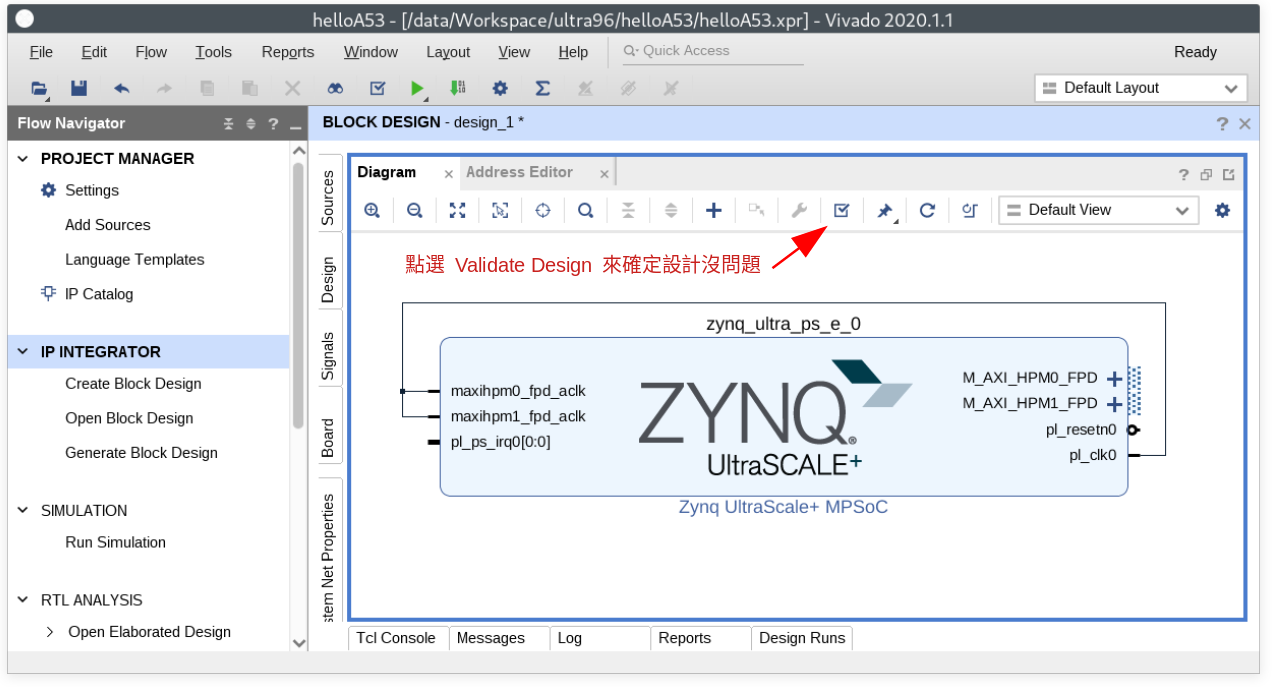

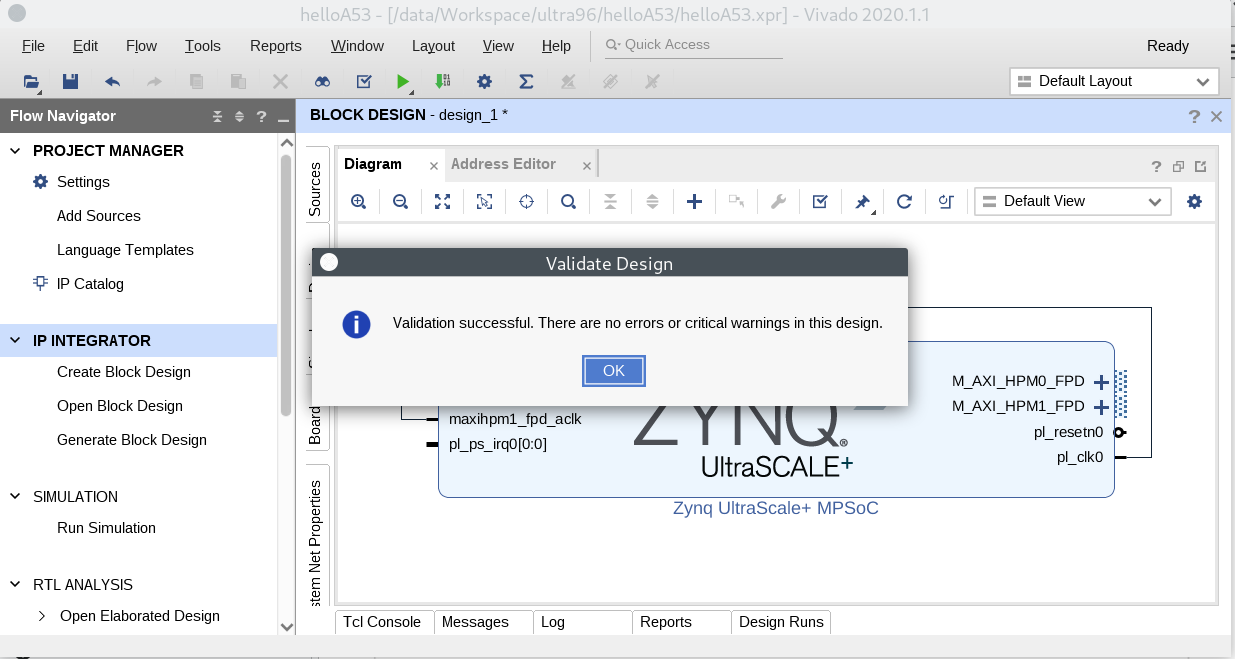

好了後,點選 Validate Design 按鈕來確認設計沒問題

沒問題的話,就讓我們來結束 Block Design 的工作吧

產生 HDL Wrapper

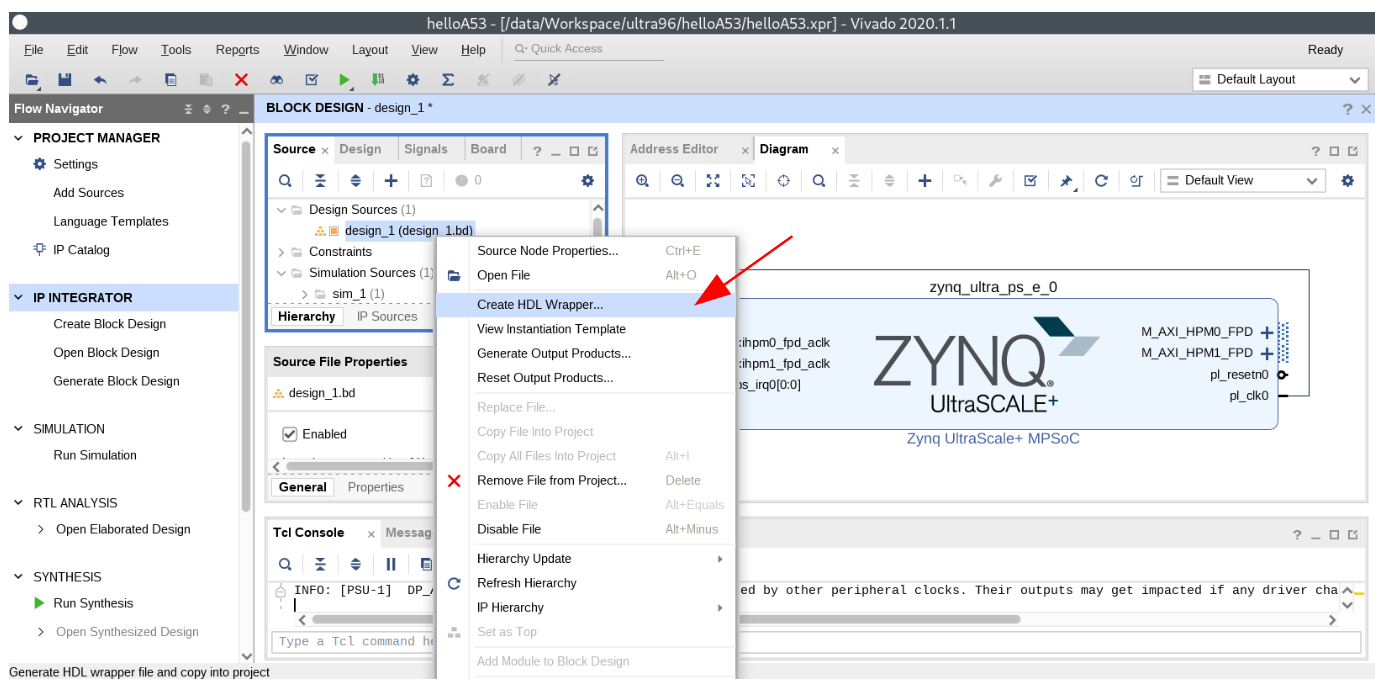

接下來我們要將剛剛用 Block Design 建立的電路變成 verilog 程式碼,因此會需要進行產生 HDL Wrapper 這個步驟。

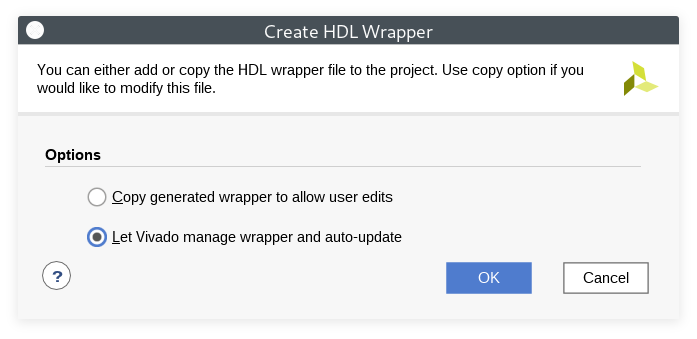

對你的 Block Design 檔案點選右鍵,選擇 Create HDL Wrapper ,它會根據你專案設定的語言 (VHDL 或是 Verilog) 來產生相對的 HDL 程式碼。

由於這次我們不需要對產出來的東西進行修改,因此選 Let Vivado manage wrapper and auto-update 即可

好了後,假設你的 Block Design 檔案叫做 design_1.bd ,那就會產生 design_1_wrapper.v 或是 design_1_wrapper.vhdl 這樣的檔案。

產生位元流 (bitstream)

前面的處理都好了後,接下來點選 Program and Debug -> Generate Bitstream 去讓 Viavado 將這個專案產生出 位元流 (bitstream) ,Zynq UltraScale+ 會在開機的時候根據 bitstream 的資訊對 FPGA 進行設定。

這個產生的過程視你的電腦強度如何而決定花多少時間,總之先來泡杯茶吧~

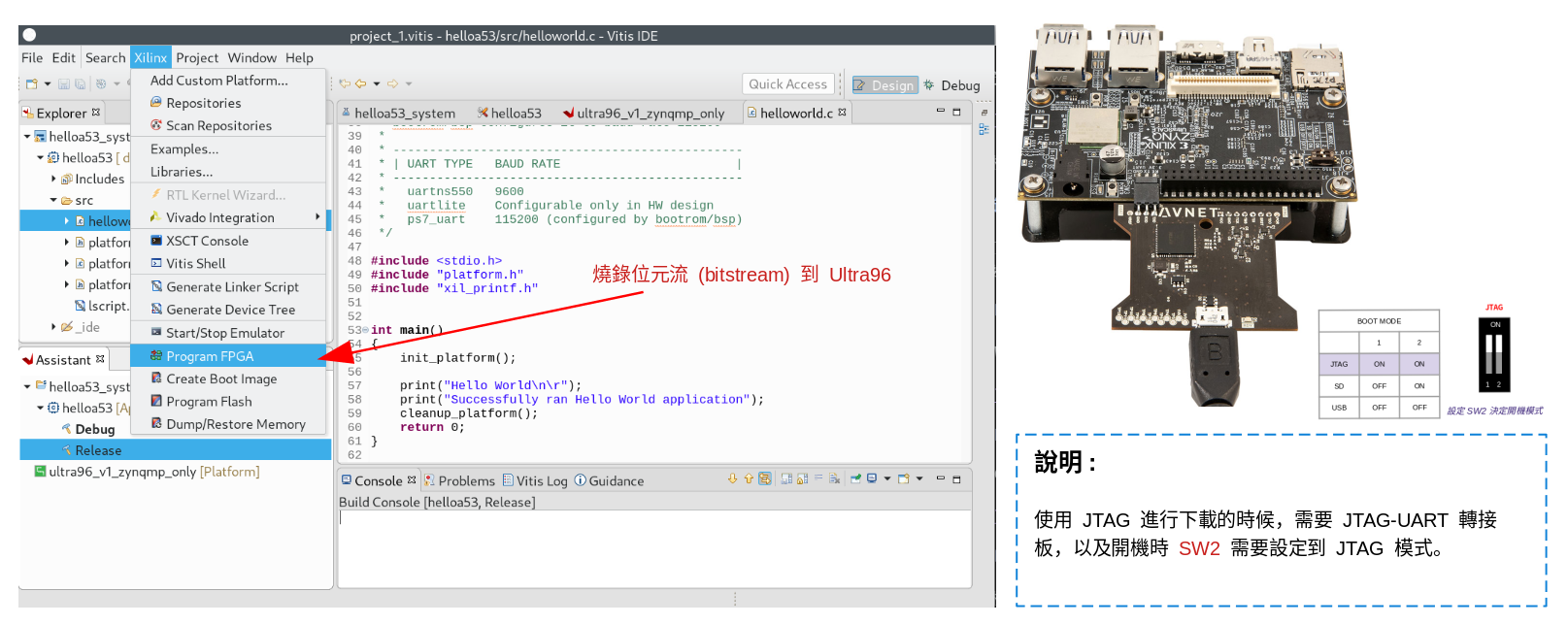

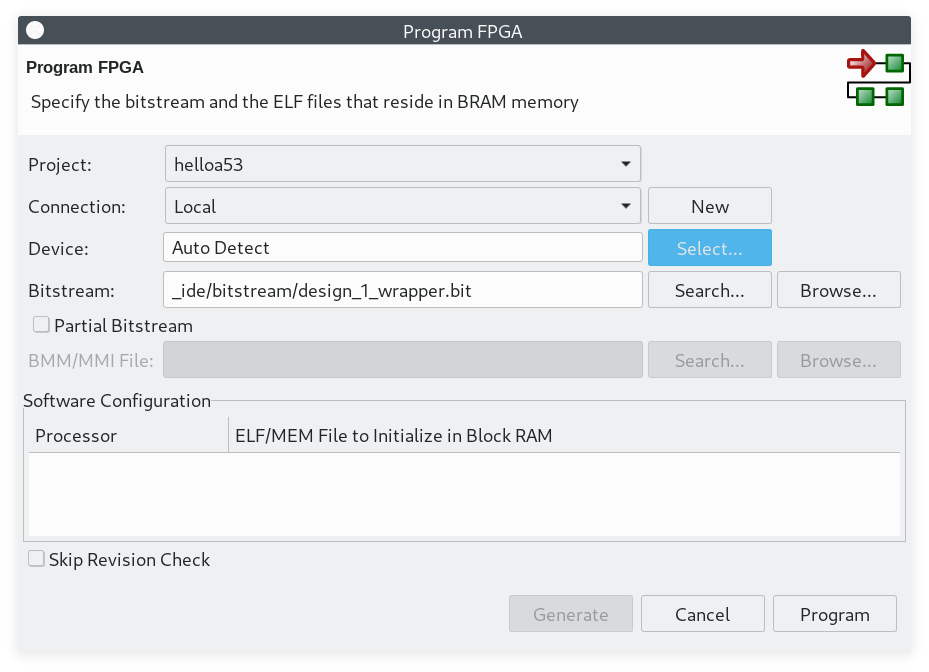

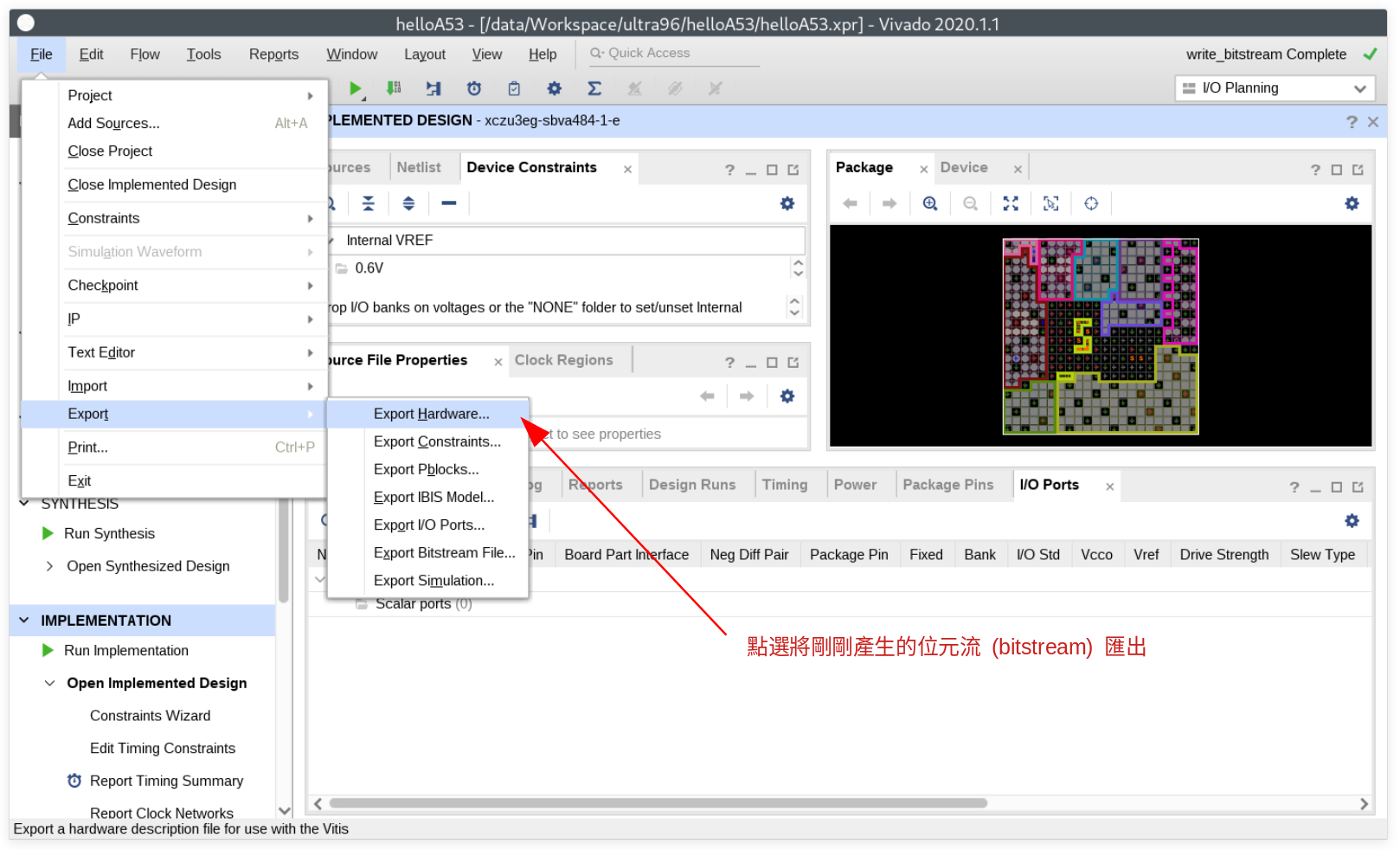

當 bitstream 完成後,我們準備執行 Xilinx SDK 來透過寫 C 語言專案來讓 Cortex-A53 可以透過 UART1 輸出訊息,因此要先將剛剛產生的硬體資訊輸出給 Xilinx SDK 去。

點選 File -> Export -> Export Hardware

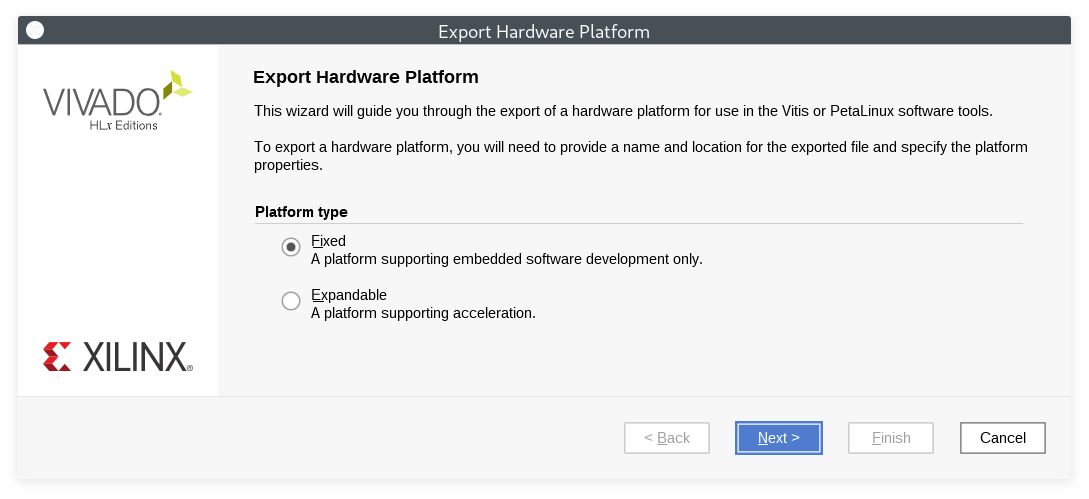

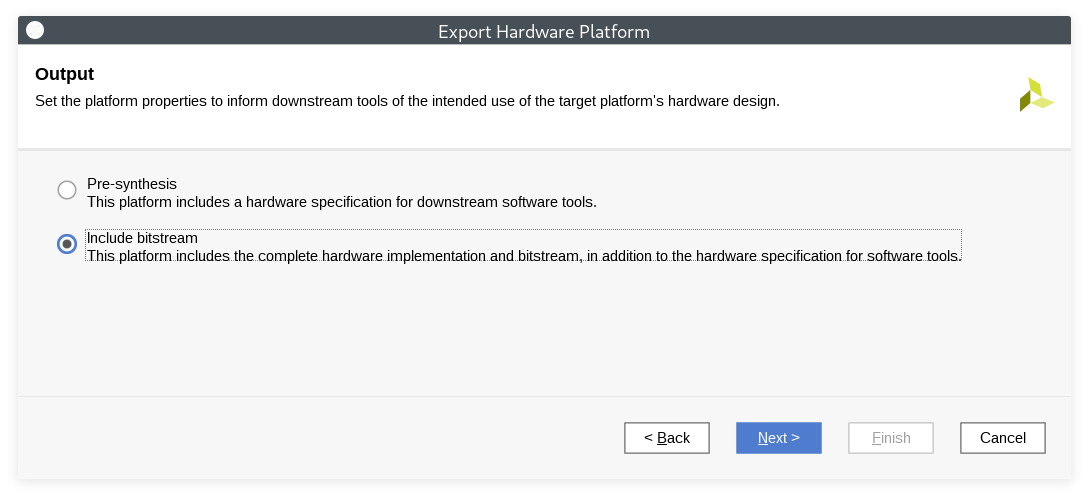

這邊我們選擇 Fixed

選擇 Include bitstream

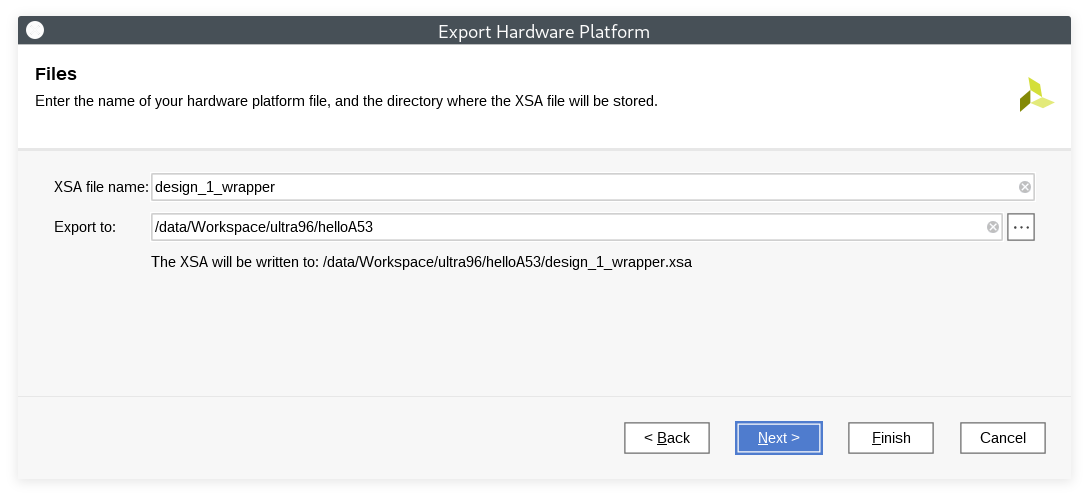

確認沒問題後,點選 Finish

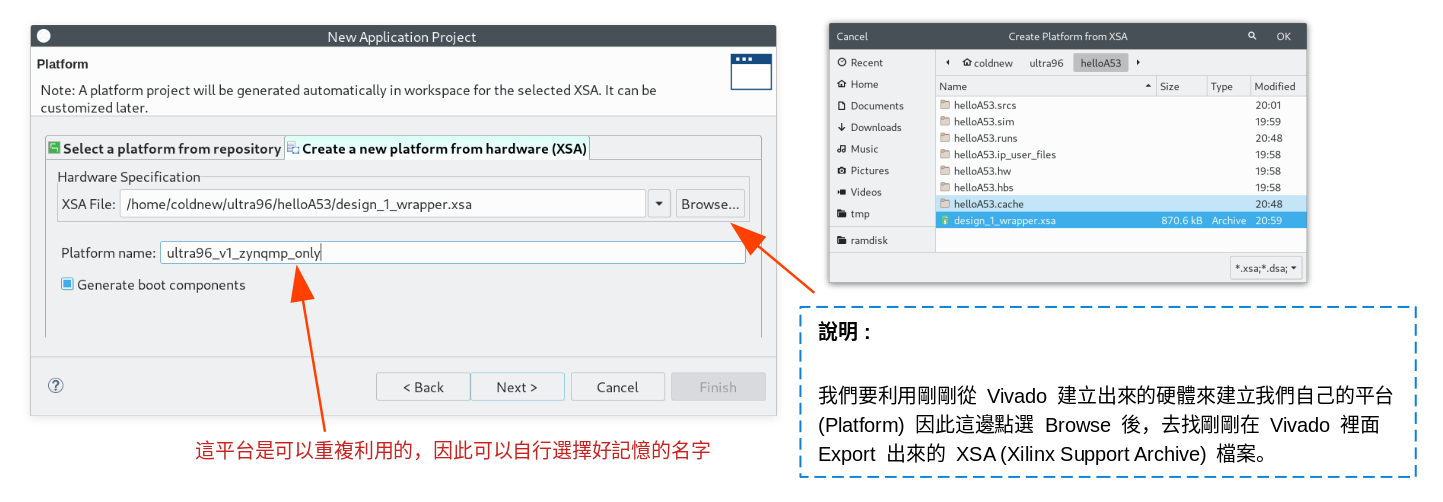

以我這邊為例,會產生一個名為 design_1_wrapper.xsa 的檔案在 /data/Workspace/ultra96/helloA53 ,這個 XSA (Xilinx Support Archive) 檔案是等等要給 Vitis 建立我們需要的平台使用。

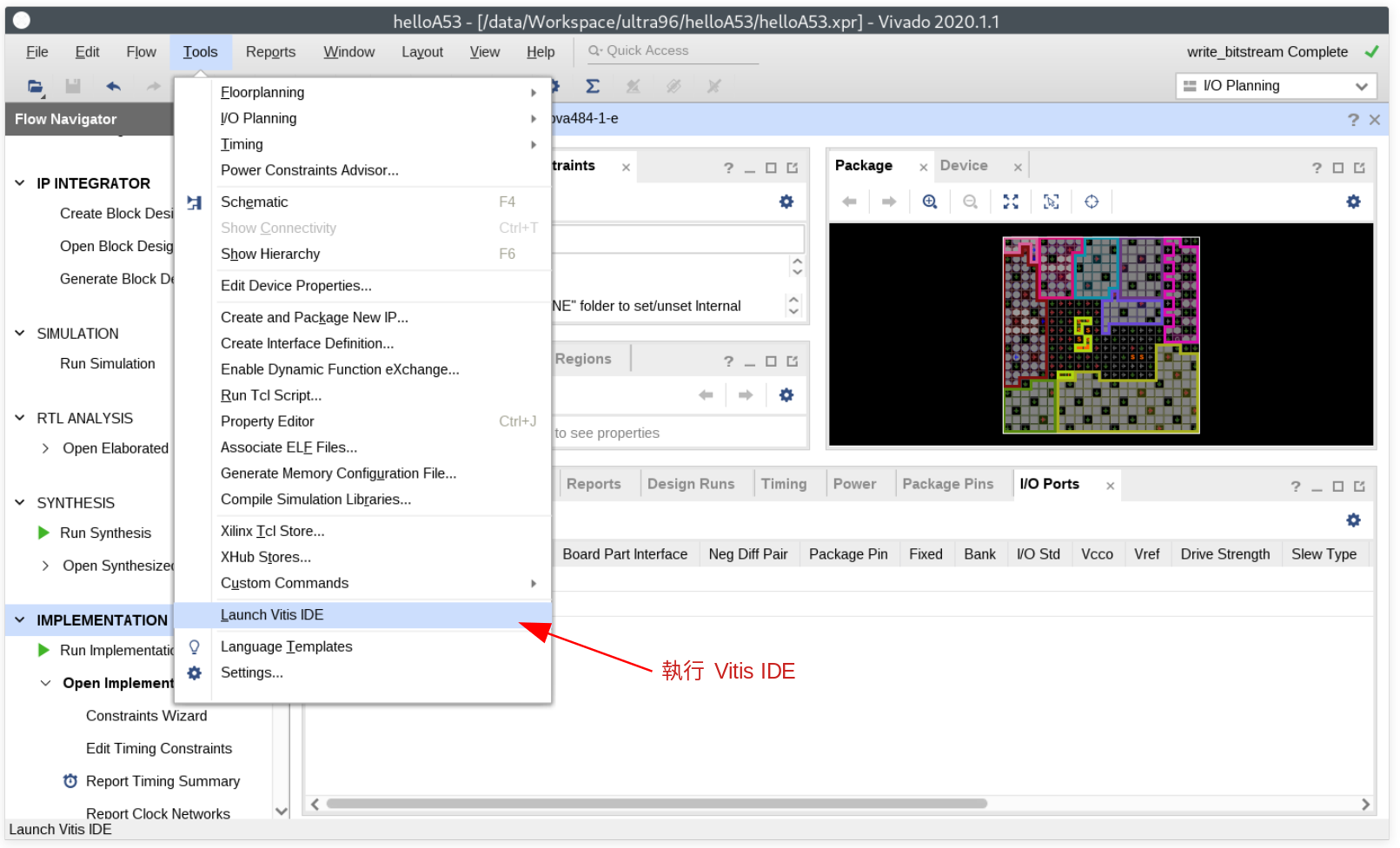

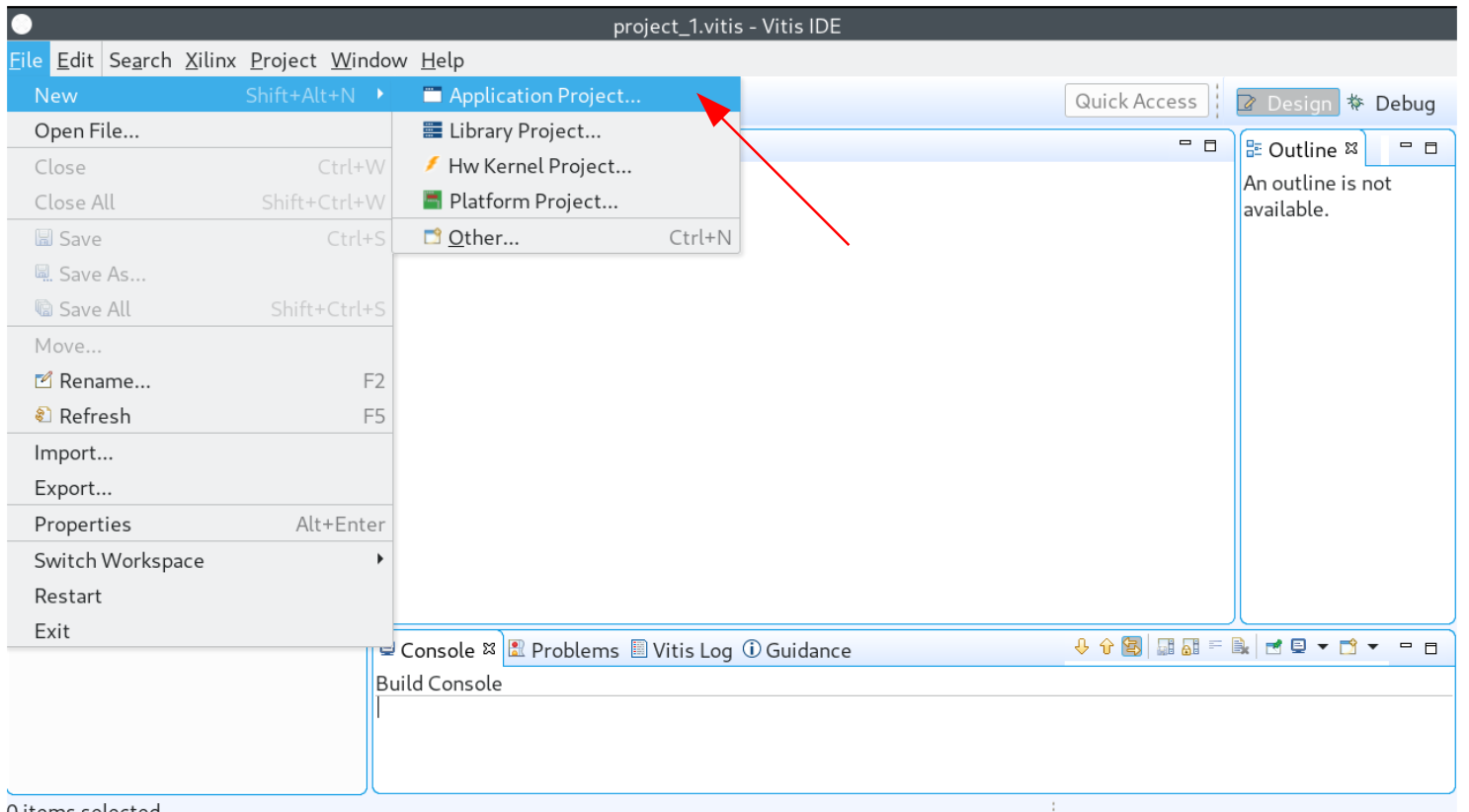

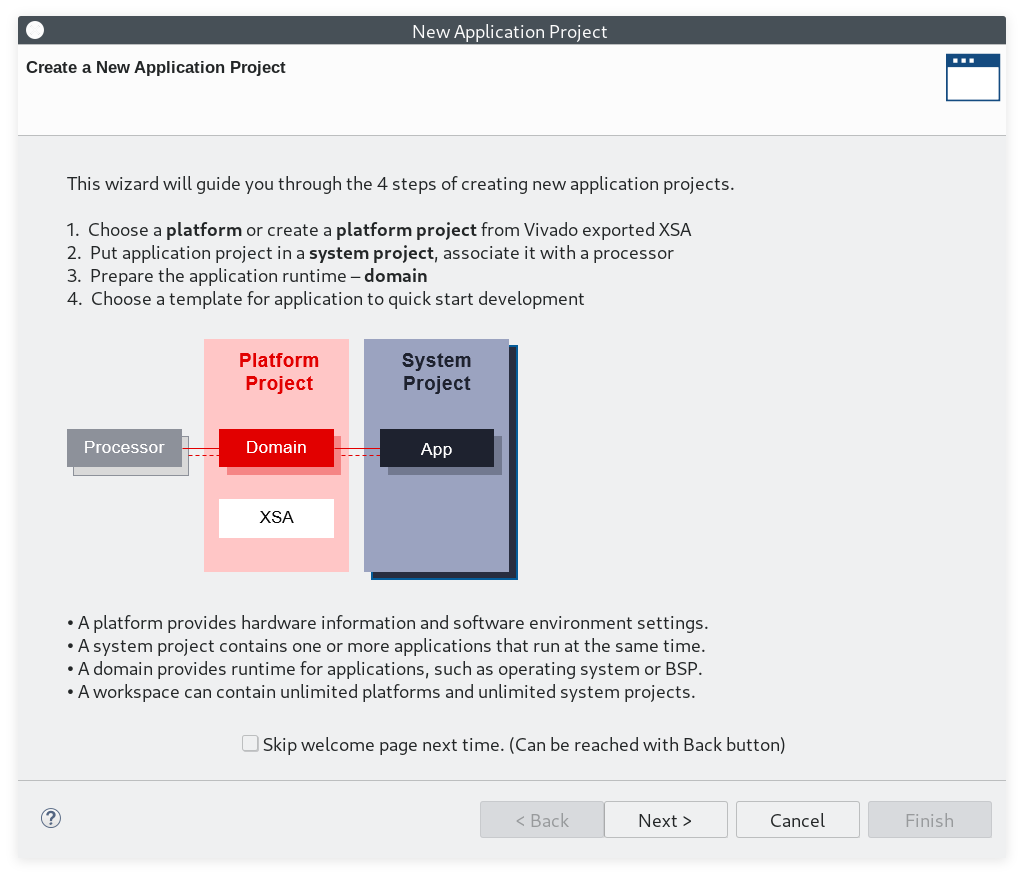

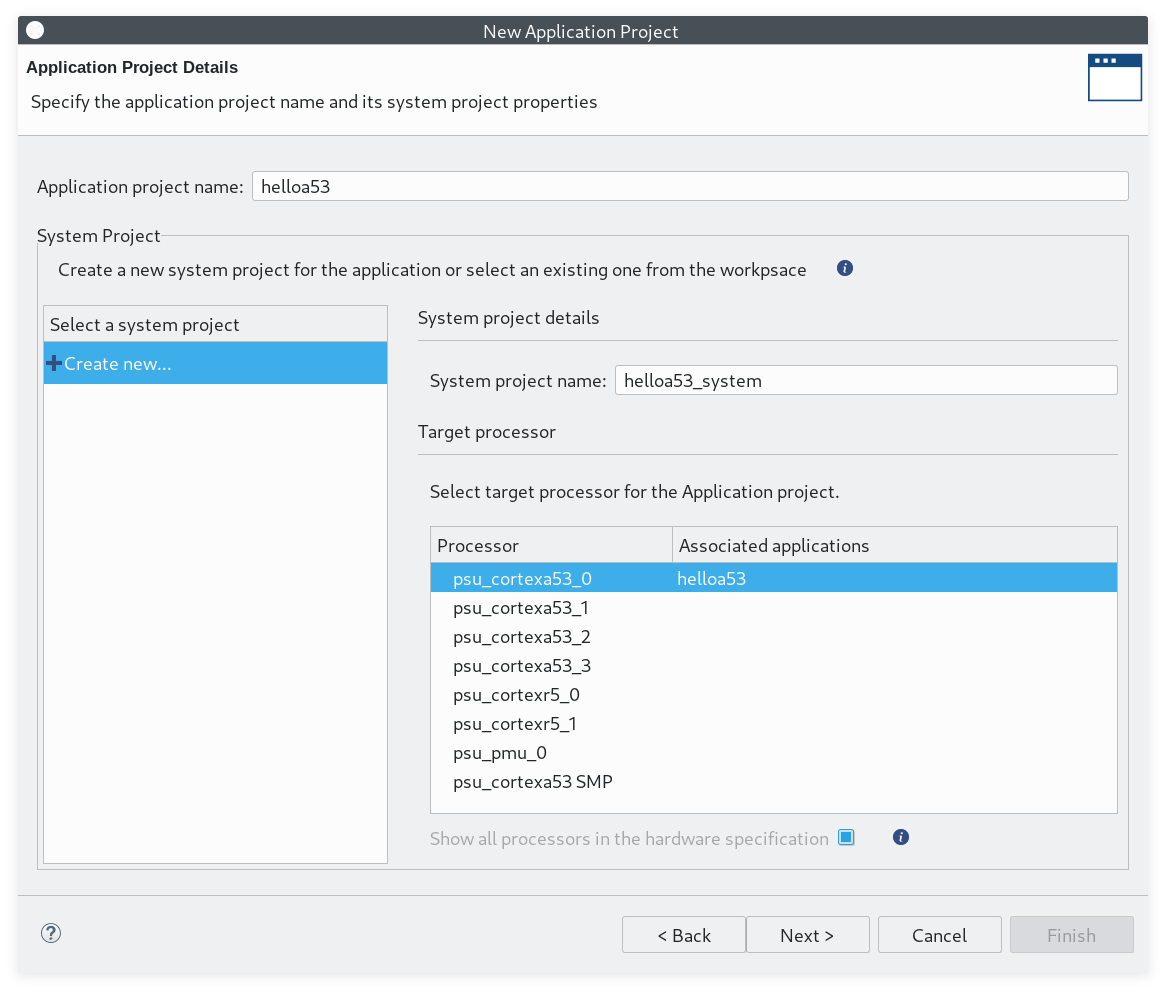

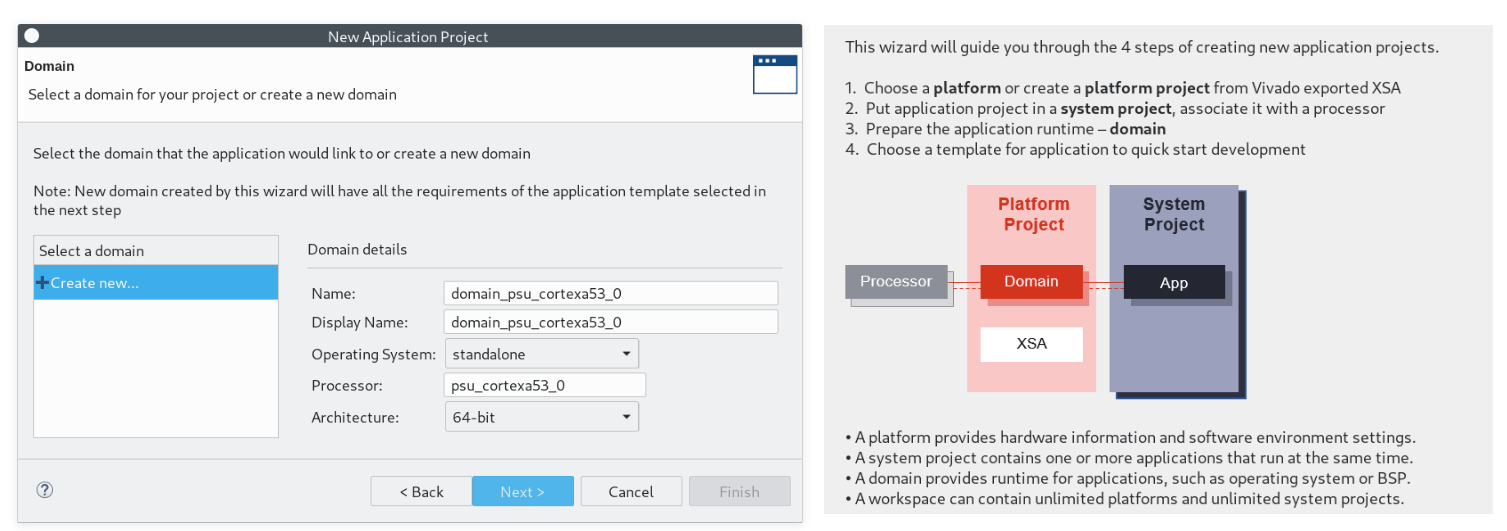

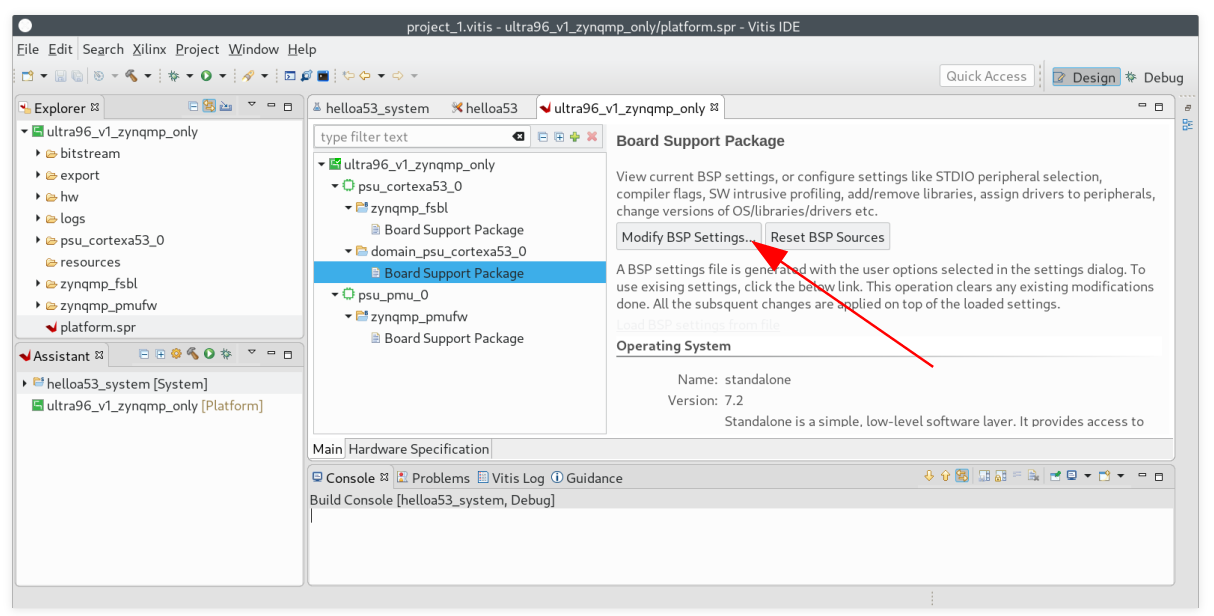

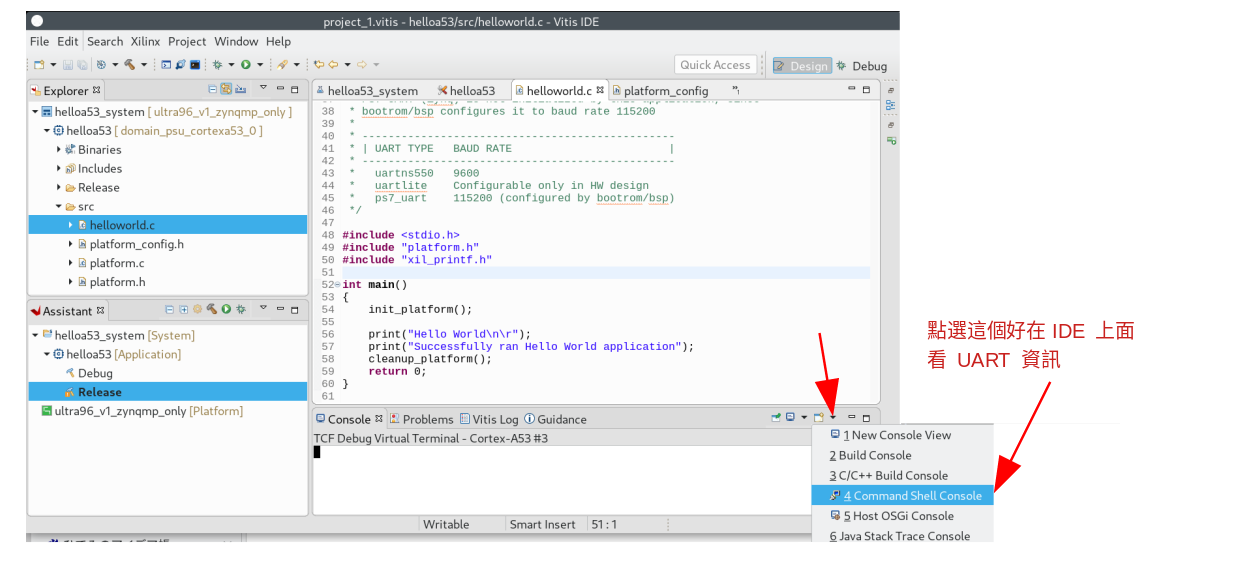

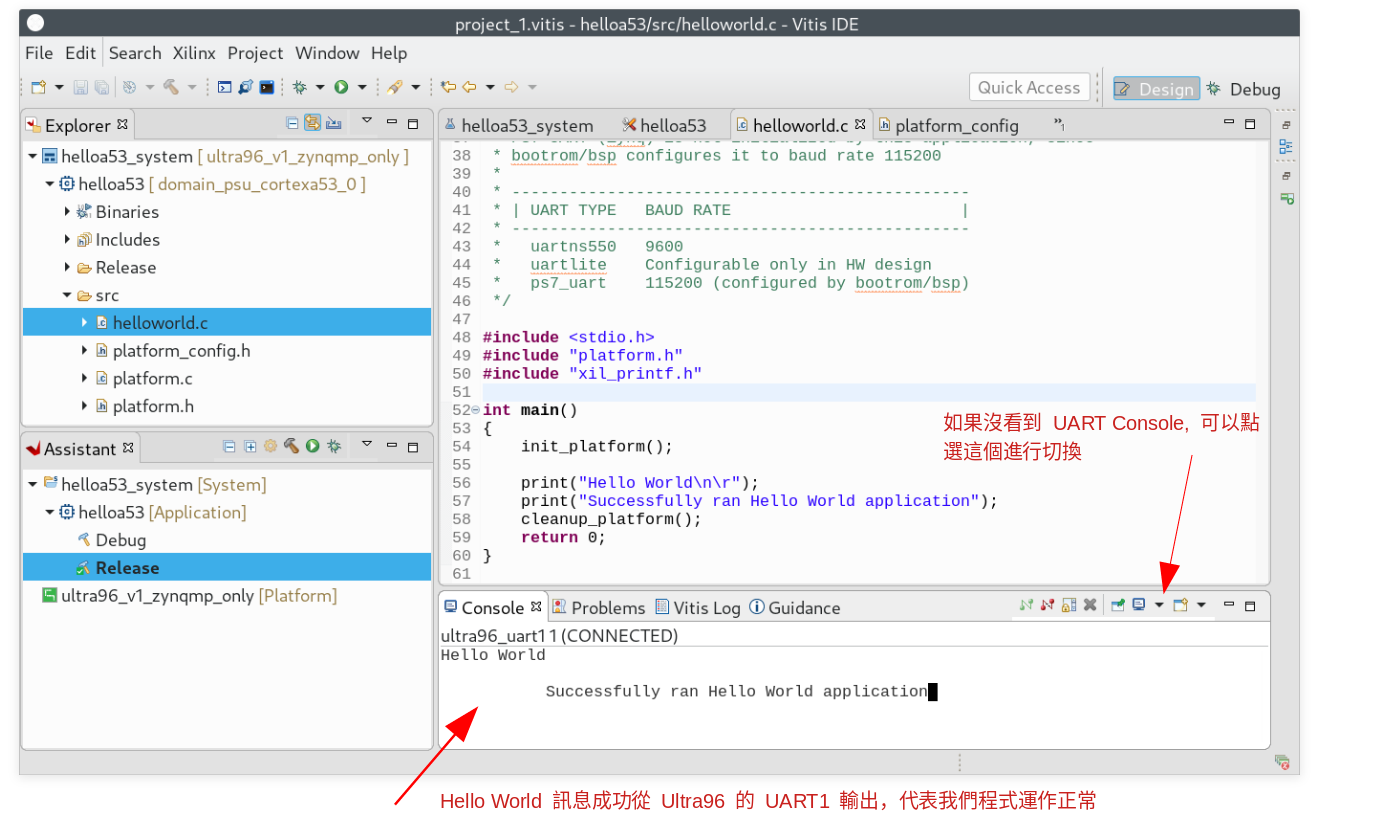

確認 OK 後,執行 Vitis IDE